# **PY32F07X Series**

# 32-bit ARM® Cortex®-M0+ Microcontrollers

# **Reference Manual**

Puya Semiconductor (Shanghai) Co., Ltd.

# Contents

| 1. | List | t of abbreviations for register                | . 23 |

|----|------|------------------------------------------------|------|

| 2. | Sys  | stem architecture                              | . 24 |

| 3. | Mei  | mory and bus architecture                      | . 25 |

|    | 3.1. | System architecture                            | . 25 |

|    | 3.2. | Memory structure                               | . 26 |

|    | 3.2. | .1. Memory Structure Introduction              | . 26 |

|    | 3.3. | Embedded SRAM                                  | . 29 |

|    | 3.4. | Boot mode                                      | .30  |

|    | 3.4. | .1. Memory physical image                      | .30  |

|    | 3.4. | .2. Embedded bootstrap program                 | . 30 |

| 4. | Em   | bedded Flash                                   | 31   |

|    | 4.1. | Flash memory main features                     | . 31 |

|    | 4.2. | Introduction to Flash memory functions         | . 31 |

|    | 4.2. | .1. Flash memory architecture                  | .31  |

|    | 4.2. | .2. Flash read operations and access latency   | . 31 |

|    | 4.2. | .3. Flash Write and Erase Operations           | . 32 |

|    | 4.3. | Flash Option Bytes                             | . 35 |

|    | 4.3. | .1. Flash option word                          | . 35 |

|    | 4.3. | .2. Flash Option Byte Write                    | . 38 |

|    | 4.4. | Flash configuration byte                       | 39   |

|    | 4.4. | .1. HSI_TRIMMING_FOR_USER                      | . 41 |

|    | 4.4. | .2. Calibration values for temperature sensors | . 42 |

|    | 4.4. | .3. HSI_4M/8M/16M/22.12M/24M_EPPARA0           | . 42 |

|    | 4.4. | .4. HSI_4M/8M/16M/22.12M/24M_EPPARA1           | . 42 |

|    | 4.4. | .5. HSI_4M/8M/16M/22.12M/24M_EPPARA2           | . 43 |

|    | 4.4. | .6. HSI_4M/8M/16M/22.12M/24M_EPPARA3           | . 43 |

|    | 4.4. | .7. HSI_4M/8M/16M/22.12M/24M_EPPARA4           | . 43 |

|    | 4.5. | Flash memory protection                        | . 44 |

|    | 4.5. | .1. Flash memory read protection               | . 44 |

|    | 4.5. | .2. Flash write protection                     | . 45 |

|    | 4.5. | .3. Option Byte Write Protect                  | . 45 |

|    | 4.6. | Flash memory interruption                      | . 45 |

|    | 4.7. | Flash Register Description                     | . 46 |

|    | 4.7. | .1. Flash Access Control Register (FLASH_ACR)  | . 46 |

|    | 4.7. | .2. Flash Key Register (FLASH_KEYR)            | . 47 |

|    | 4.7. | .3. Flash Option Key Register (FLASH_OPTKEYR)  | . 47 |

|    | 4.7. | .4. Flash Status Register (FLASH_SR)           | . 48 |

|    | 4.7. | .5. Flash Control Register (FLASH_CR)          | . 48 |

| 4    | 4.7.6.  | Flash Options Register (FLASH_OPTR)                                   | 51 |

|------|---------|-----------------------------------------------------------------------|----|

| 4    | 4.7.7.  | Flash BORCR Address Register (FLASH_BORCR)                            | 52 |

| 4    | 4.7.8.  | Flash WRP Address Register (FLASH_WRPR)                               | 52 |

| 4    | 4.7.9.  | Flash Sleep Time Configuration Register (FLASH_STCR)                  | 54 |

| 4    | 4.7.10. | Flash TS0 register (FLASH_TS0)                                        | 54 |

| 4    | 4.7.11. | Flash TS1 Register (FLASH_TS1)                                        | 55 |

| 4    | 4.7.12. | Flash TS2P Register (FLASH_TS2P)                                      | 56 |

| 4    | 4.7.13. | Flash TPS3 register (FLASH_TPS3)                                      | 56 |

| 4    | 4.7.14. | Flash TS3 register (FLASH_TS3)                                        | 57 |

| 4    | 4.7.15. | Flash Page Erase (PAGE ERASE) TPE Register (FLASH_PERTPE)             | 57 |

| 4    | 4.7.16. | Flash SECTOR/MASS ERASE TPE Register (FLASH_SMERTPE)                  | 58 |

| 4    | 4.7.17. | Flash PROGRAM TPE register (FLASH_PRGTPE)                             | 58 |

| 4    | 4.7.18. | Flash PRE-PROGRAM TPE Register (FLASH_PRETPE)                         | 59 |

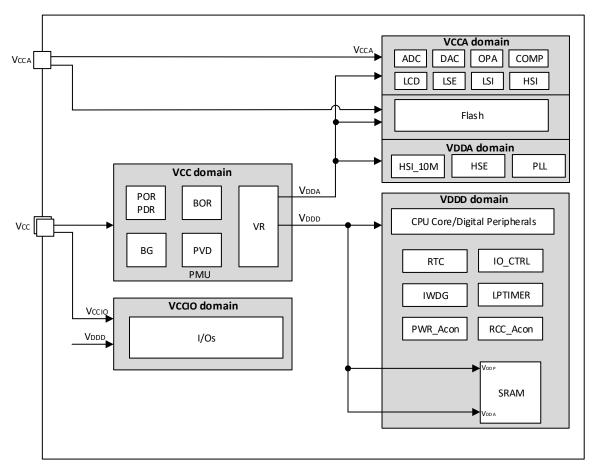

| 5. l | Power o | control                                                               | 60 |

| 5.1  | . Po    | wer supply                                                            | 60 |

| į    | 5.1.1.  | Power Supply Block Diagram                                            | 60 |

| 5.2  | . Vo    | tage regulator                                                        | 61 |

| 5.3  | B. Po   | wer monitoring                                                        | 61 |

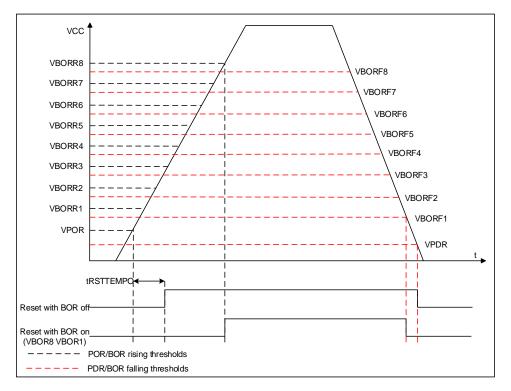

| į    | 5.3.1.  | Power-0n reset (POR) / Power-down reset (PDR) / Brown-out reset (BOR) | 61 |

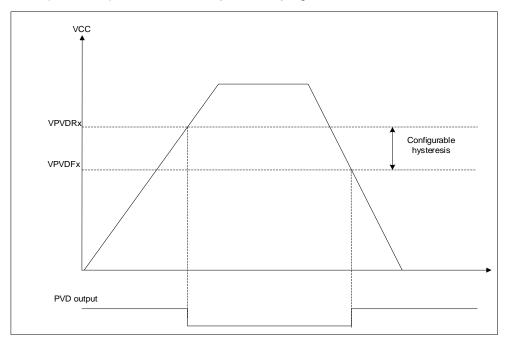

| į    | 5.3.2.  | Programmable Voltage Detector (PVD)                                   | 62 |

| 6. l | Low-po  | wer control                                                           | 63 |

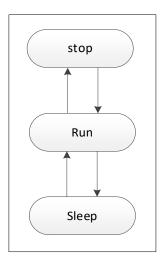

| 6.1  | . Lo    | w Power Mode                                                          | 63 |

| (    | 6.1.1.  | Introduction to Low Power Mode                                        | 63 |

| (    | 6.1.2.  | Low Power Mode Switch                                                 | 64 |

| (    | 6.1.3.  | Functions in each operating mode                                      | 64 |

| 6.2  | 2. Sle  | ep mode                                                               | 65 |

| (    | 6.2.1.  | Entering sleep mode                                                   | 65 |

| (    | 6.2.2.  | Exit sleep mode                                                       | 65 |

| 6.3  | Sto     | p mode                                                                | 66 |

| (    | 6.3.1.  | Enter Stop mode                                                       | 66 |

| (    | 6.3.2.  | Exiting Stop Mode                                                     | 67 |

| 6.4  | l. Re   | duced system clock frequency                                          | 68 |

| 6.5  | . Pei   | ipheral clock gating                                                  | 68 |

| 6.6  | i. Po   | wer Management Registers                                              | 68 |

| (    | 6.6.1.  | Power Control Register 1 (PWR_CR1)                                    | 68 |

| (    | 6.6.2.  | Power Control Register 2 (PWR_CR2)                                    | 69 |

| (    | 6.6.3.  | Power Supply Status Register (PWR_SR)                                 | 70 |

| 7. I | Reset   |                                                                       | 72 |

| 7.1  |         | set source                                                            |    |

| -    | 7.1.1.  | Power Reset                                                           | 72 |

|    | 7.1.2.   | System reset                                                    | 72  |

|----|----------|-----------------------------------------------------------------|-----|

|    | 7.1.3.   | NRST pin (External reset)                                       | 72  |

|    | 7.1.4.   | Watchdog reset                                                  | 72  |

|    | 7.1.5.   | Software reset                                                  | 73  |

|    | 7.1.6.   | Option byte loader reset                                        | 73  |

| 8. | Clocks   |                                                                 | 74  |

| 8  | 3.1. Cld | ock source                                                      | 74  |

|    | 8.1.1.   | External high-speed clock HSE                                   | 74  |

|    | 8.1.2.   | Internal high-speed clock HSI                                   | 74  |

|    | 8.1.3.   | Internal low-speed clock LSI                                    | 74  |

|    | 8.1.4.   | HSI10M Clock                                                    | 75  |

|    | 8.1.5.   | PLL                                                             | 75  |

|    | 8.1.6.   | LSE Clock                                                       | 75  |

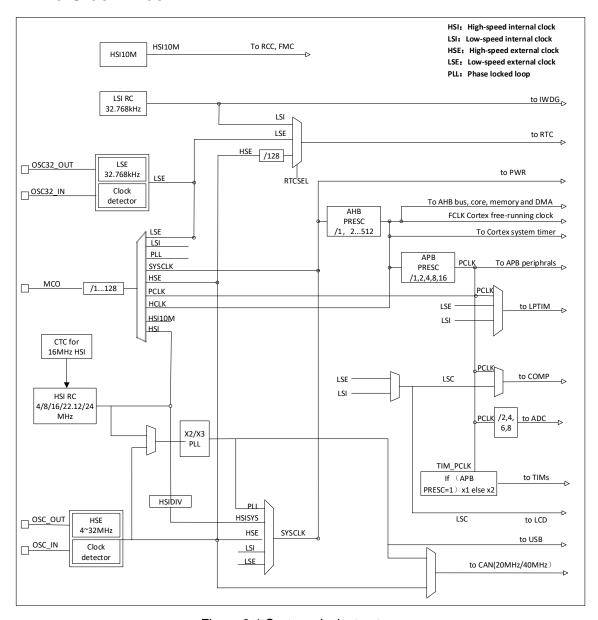

| 8  | 3.2. Th  | e Clock Tree                                                    | 76  |

| 8  | 3.3. Clo | ock Safety System (CSS)                                         | 76  |

|    | 8.3.1.   | Clock Configuration and Stateful Security                       | 76  |

|    | 8.3.2.   | Clock source HSE monitoring                                     | 77  |

|    | 8.3.3.   | Clock source LSE monitoring                                     | 77  |

| 8  | 3.4. Ou  | tput Clock Capability                                           | 78  |

| 8  | .5. Re   | set/Clock Register                                              | 78  |

|    | 8.5.1.   | Clock Control Register (RCC_CR)                                 | 78  |

|    | 8.5.2.   | Internal clock source calibration register (RCC_ICSCR)          | 80  |

|    | 8.5.3.   | Clock Configuration Register (RCC_CFGR)                         | 81  |

|    | 8.5.4.   | PLL configuration register (RCC_PLLCFGR)                        | 83  |

|    | 8.5.5.   | External Clock Source Control Register (RCC_ECSCR)              | 84  |

|    | 8.5.6.   | Clock interrupt enable register (RCC_CIER)                      | 85  |

|    | 8.5.7.   | Clock Interrupt Flag Register (RCC_CIFR)                        | 86  |

|    | 8.5.8.   | Clock Interrupt Clear Register (RCC_CICR)                       | 88  |

|    | 8.5.9.   | I/O Interface Reset Register (RCC_IOPRSTR)                      | 89  |

|    | 8.5.10.  | AHB Peripheral Reset Register (RCC_AHBRSTR)                     | 89  |

|    | 8.5.11.  | APB Peripheral Reset Register 1 (RCC_APBRSTR1)                  | 90  |

|    | 8.5.12.  | APB Peripheral Reset Register 2 (RCC_APBRSTR2)                  | 92  |

|    | 8.5.13.  | I/O interface clock enable register (RCC_IOPENR)                | 94  |

|    | 8.5.14.  | AHB Peripheral Clock Enable Register (RCC_AHBENR)               | 95  |

|    | 8.5.15.  | APB Peripheral Clock Enable Register 1 (RCC_APBENR1)            | 96  |

|    | 8.5.16.  | APB Peripheral Clock Enable Register 2 (RCC_APBENR2)            | 98  |

|    | 8.5.17.  | Peripheral Independent Clock Configuration Register (RCC_CCIPR) | 100 |

|    | 8.5.18.  | RTC Domain Control Register (RCC_BDCR)                          | 101 |

|    | 8.5.19.  | Control/Status Register (RCC_CSR)                               | 102 |

| 9. | Clock C  | Calibration Controller (CTC)                                    | 105 |

| 9.  | 1.    | Intro | oduction                                                                     | 105 |

|-----|-------|-------|------------------------------------------------------------------------------|-----|

| 9.  | 2.    | СТС   | Main Characteristics                                                         | 105 |

| 9.  | 3.    | СТС   | Functional Description                                                       | 105 |

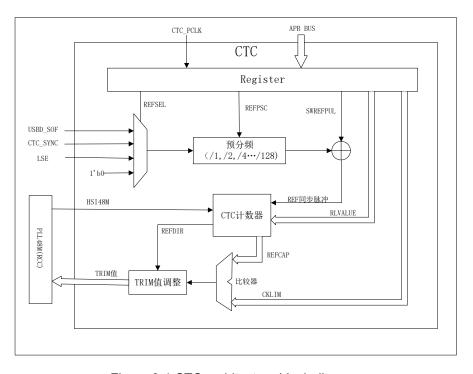

|     | 9.3.1 |       | CTC Block Diagram                                                            | 105 |

|     | 9.3.2 | 2.    | REF Synchronized Pulse Generator                                             | 106 |

|     | 9.3.3 | 3.    | CTC Calibration Counter                                                      | 106 |

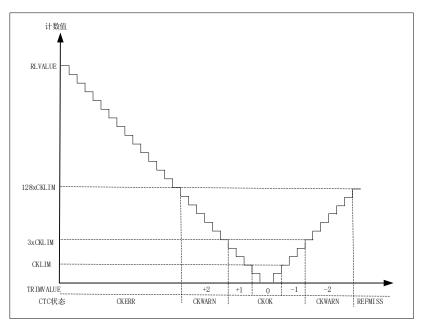

|     | 9.3.4 | ١.    | Frequency evaluation and automatic calibration process                       | 107 |

|     | 9.3.5 | j.    | Software Programming Guide                                                   | 108 |

| 9.  | 4.    | СТС   | Register                                                                     | 108 |

|     | 9.4.1 |       | CTC control register 0 (CTC_CTL0)                                            | 108 |

|     | 9.4.2 | 2.    | CTC control register 1 (CTC_CTL1)                                            | 110 |

|     | 9.4.3 | 3.    | CTC Status Register (CTC_SR)                                                 | 111 |

|     | 9.4.4 | ١.    | CTC interrupt clear register (CTC_INTC)                                      | 114 |

| 10. | Ge    | ener  | al Purpose I/O (GPIO)                                                        | 116 |

| 10  | ).1.  | In    | troduction                                                                   | 116 |

| 10  | ).2.  | G     | eneral Purpose IO Functional Description                                     | 116 |

| 10  | ).3.  | G     | eneral Purpose IO Functional Description                                     | 116 |

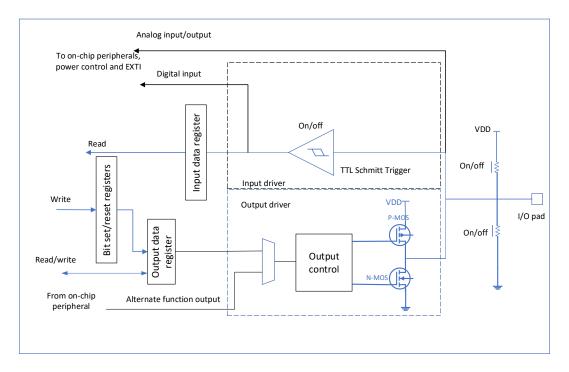

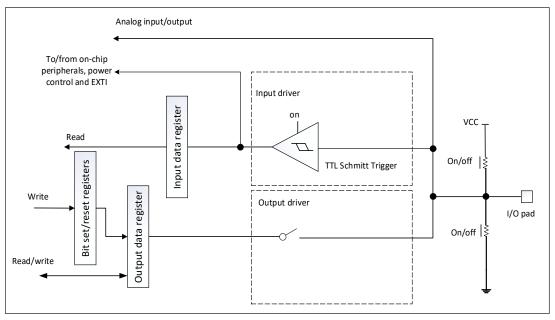

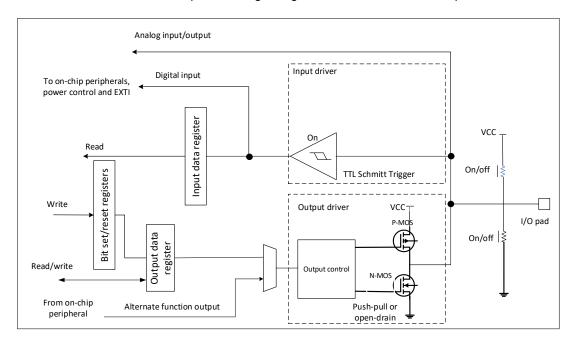

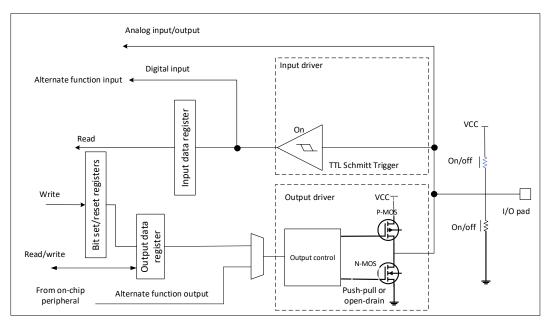

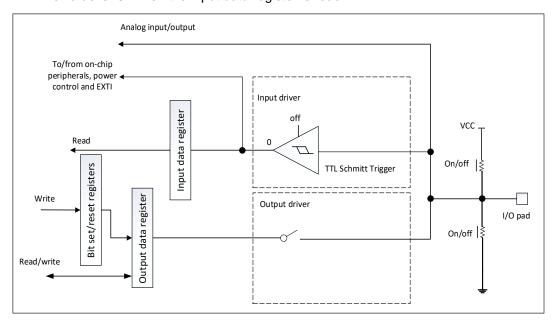

|     | 10.3  | .1.   | General Purpose I/O (GPIO)                                                   | 117 |

|     | 10.3  | .2.   | I/O pin-multiplexing function multiplexing and mapping                       | 117 |

|     | 10.3  | .3.   | I/O Control Registers                                                        | 118 |

|     | 10.3  | .4.   | I/O Data Register                                                            | 119 |

|     | 10.3  | .5.   | I/O data processing by bit                                                   | 119 |

|     | 10.3  | .6.   | I/O Multiplexing Function Input/Output Mode Configuration                    | 119 |

|     | 10.3  | .7.   | External interrupt/wakeup line                                               | 120 |

|     | 10.3  | .8.   | I/O Input Configuration                                                      | 120 |

|     | 10.3  | .9.   | I/O Output Configuration                                                     | 120 |

|     | 10.3  | .10.  | Multiplexing Function Configuration                                          | 121 |

|     | 10.3  | .11.  | Analog Configuration                                                         | 122 |

|     | 10.3  | .12.  | Using the HSE/LSE pins as GPIOs                                              | 122 |

| 10  | ).4.  | G     | PIO registers                                                                | 124 |

|     | 10.4  | .1.   | GPIO port mode register (GPIOx_MODER) (x=A, B, C, F)                         | 124 |

|     | 10.4  | .2.   | GPIO port output type register (GPIOx_OTYPER) ( $x = A, B, C, F$ )           | 124 |

|     | 10.4  | .3.   | GPIO port output speed register (GPIOx_OSPEEDR) ( $x = A, B, C, F$ )         | 125 |

|     | 10.4  | .4.   | GPIO port pull-down register (GPIOx_PUPDR) (x = A, B, C, F)                  | 125 |

|     | 10.4  | .5.   | GPIO port input data register (GPIOx_IDR) (x = A, B, C, F)                   | 126 |

|     | 10.4  | .6.   | GPIO port output data register (GPIOx_ODR) (x = A, B, C, F)                  | 126 |

|     | 10.4  | .7.   | GPIO port bit set/reset register (GPIOx_BSRR) (x = A, B, C, F)               | 127 |

|     | 10.4  | .8.   | GPIO Port Configuration Lock Register (GPIOx_LCKR) (x = A, B, C, F)          | 127 |

|     | 10.4  | .9.   | GPIO multiplexing function register (low) (GPIOx_AFRL) ( $x = A, B, C, F$ )  | 128 |

|     | 10.4  | 10.   | GPIO multiplexing function register (high) (GPIOx AFRH) ( $x = A, B, C, F$ ) | 129 |

| 10.4.11.   | GPIO Port Bit Reset Register (GPIOx_BRR) (x = A, B, C, F) | 130 |

|------------|-----------------------------------------------------------|-----|

| 11. Syste  | m Configuration Controller (SYSCFG)                       | 131 |

| 11.1. S    | ystem Configuration Register                              | 131 |

| 11.1.1.    | SYSCFG Configuration Register 1 (SYSCFG_CFGR1)            | 131 |

| 11.1.2.    | SYSCFG Configuration Register 2 (SYSCFG_CFGR2)            | 133 |

| 11.1.3.    | SYSCFG Configuration Register 3 (SYSCFG_CFGR3)            | 136 |

| 11.1.4.    | SYSCFG Configuration Register 4 (SYSCFG_CFGR4)            | 138 |

| 11.1.5.    | GPIOA filter enable (PA_ENS)                              | 138 |

| 11.1.6.    | GPIOB filter enable (PB_ENS)                              | 139 |

| 11.1.7.    | GPIOC filter enable (PC_ENS)                              | 139 |

| 11.1.8.    | GPIOF filter enable (PF_ENS)                              | 140 |

| 11.1.9.    | I2C configuration register (SYSCFG_EIIC)                  | 140 |

| 12. Direct | Memory Access (DMA)                                       | 142 |

| 12.1. Ir   | ntroduction                                               | 142 |

| 12.2. D    | MA main features                                          | 142 |

| 12.3. D    | MA Function Description                                   | 143 |

| 12.3.1.    | DMA processing                                            | 143 |

| 12.3.2.    | Arbiter                                                   | 143 |

| 12.3.3.    | DMA channel                                               | 144 |

| 12.3.4.    | Data Transfer Width/Alignment/Size End                    | 147 |

| 12.3.5.    | Error management                                          | 149 |

| 12.3.6.    | DMA interrupt                                             |     |

| 12.3.7.    | DMA Peripheral Request Mapping                            |     |

| 12.4. D    | MA registers                                              |     |

| 12.4.1.    | DMA Interrupt Status Register (DMA_ISR)                   | 150 |

| 12.4.2.    | DMA Interrupt Flag Bit Clear Register (DMA_IFCR)          |     |

| 12.4.3.    | DMA Channel 1 Configuration Register (DMA_CCR1)           |     |

| 12.4.4.    | DMA channel 1 data transfer count register (DMA_CNDTR1)   |     |

| 12.4.5.    | DMA Channel 1 Peripheral Address Register (DMA_CPAR1)     | 158 |

| 12.4.6.    | DMA channel 1 memory address register (DMA_CMAR1)         | 159 |

| 12.4.7.    | DMA Channel 2 Configuration Register (DMA_CCR2)           | 159 |

| 12.4.8.    | DMA Channel 2 Data Transfer Count Register (DMA_CNDTR2)   | 161 |

| 12.4.9.    | DMA Channel 2 Peripheral Address Register (DMA_CPAR2)     |     |

| 12.4.10.   | DMA channel 2 memory address register (DMA_CMAR2)         | 162 |

| 12.4.11.   | DMA Channel 3 Configuration Register (DMA_CCR3)           | 163 |

| 12.4.12.   | DMA Channel 3 Data Transfer Count Register (DMA_CNDTR3)   | 164 |

| 12.4.13.   | DMA Channel 3 Peripheral Address Register (DMA_CPAR3)     | 165 |

| 12.4.14.   | DMA Channel 3 Memory Address Register (DMA_CMAR3)         |     |

| 12.4.15.   | DMA Channel 4 Configuration Register (DMA_CCR4)           | 166 |

| 12.4.16.   | DMA channel 4 data transfer count register (DMA_CNDTR4)   | 168 |

| 12   | 2.4.17. | DMA Channel 4 Peripheral Address Register (DMA_CPAR4) | 168 |

|------|---------|-------------------------------------------------------|-----|

| 12   | 2.4.18. | DMA Channel 4 Memory Address Register (DMA_CMAR4)     | 169 |

| 12   | 2.4.19. | DMA Channel 5 Configuration Register (DMA_CCR5)       | 169 |

| 12   | 2.4.20. | DMA channel 5 transfer count register (DMA_CNDTR5)    | 171 |

| 12   | 2.4.21. | DMA Channel 5 Peripheral Address Register (DMA_CPAR5) | 171 |

| 12   | 2.4.22. | DMA Channel 5 Memory Address Register (DMA_CMAR5)     | 172 |

| 12   | 2.4.23. | DMA Channel 6 Configuration Register (DMA_CCR6)       | 172 |

| 12   | 2.4.24. | DMA Channel 6 Transmit Count Register (DMA_CNDTR6)    | 174 |

| 12   | 2.4.25. | DMA Channel 6 Peripheral Address Register (DMA_CPAR6) | 175 |

| 12   | 2.4.26. | DMA Channel 6 Memory Address Register (DMA_CMAR6)     | 175 |

| 12   | 2.4.27. | DMA Channel 7 Configuration Register (DMA_CCR7)       | 176 |

| 12   | 2.4.28. | DMA channel 7 transfer count register (DMA_CNDTR7)    | 177 |

| 12   | 2.4.29. | DMA Channel 7 Peripheral Address Register (DMA_CPAR7) | 178 |

| 12   | 2.4.30. | DMA Channel 7 Memory Address Register (DMA_CMAR7)     | 178 |

| 13.  | Interru | upts and Events                                       | 180 |

| 13.1 | . N     | ested Vector Interrupt Controller (NVIC)              | 180 |

| 13   | 3.1.1.  | Main characteristics                                  | 180 |

| 13   | 3.1.2.  | SysTick Calibration Value Registers                   | 180 |

| 13   | 3.1.3.  | Interrupt and Exception Vector                        | 180 |

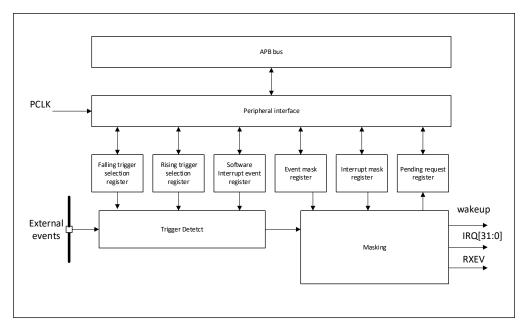

| 13.2 | . Е     | xternal Interrupt/Event Controller (EXTI)             | 181 |

| 13   | 3.2.1.  | EXTI Key Features                                     | 181 |

| 13   | 3.2.2.  | EXTI Block Diagram                                    | 182 |

| 13   | 3.2.3.  | Interruption management                               | 182 |

| 13   | 3.2.4.  | Functional Description                                | 183 |

| 13   | 3.2.5.  | Hardware Interrupt Selection                          | 183 |

| 13   | 3.2.6.  | Hardware event selection                              | 183 |

| 13   | 3.2.7.  | Software interrupt/event selection                    | 184 |

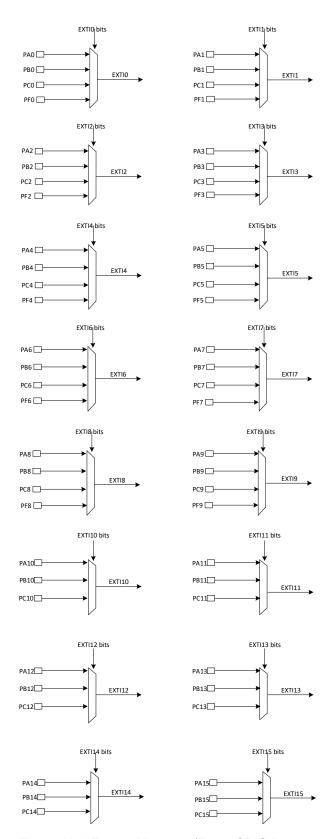

| 13   | 3.2.8.  | EXTI Selector                                         | 184 |

| 13.3 | . Е     | XTI register                                          | 186 |

| 13   | 3.3.1.  | Rising edge trigger select register (EXTI_RTSR)       | 186 |

| 13   | 3.3.2.  | Falling edge trigger select register (EXTI_FTSR)      | 188 |

| 13   | 3.3.3.  | Software Interrupt Event Register (EXTI_SWIER)        | 190 |

| 13   | 3.3.4.  | Pending Register (EXTI_PR)                            | 194 |

| 13   | 3.3.5.  | External Interrupt Select Register 1 (EXTI_EXTICR1)   | 198 |

| 13   | 3.3.6.  | External Interrupt Select Register 2 (EXTI_EXTICR2)   | 199 |

| 13   | 3.3.7.  | External Interrupt Select Register 3 (EXTI_EXTICR3)   | 200 |

| 13   | 3.3.8.  | External Interrupt Select Register 4 (EXTI_EXTICR4)   | 201 |

| 13   | 3.3.9.  | Interrupt Mask Register (EXTI_IMR)                    | 202 |

| 13   | 3.3.10. | Event Mask Register (EXTI_EMR)                        | 205 |

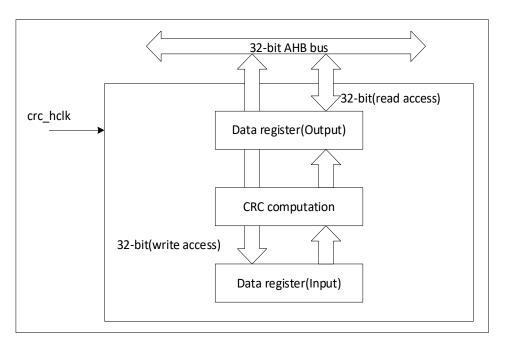

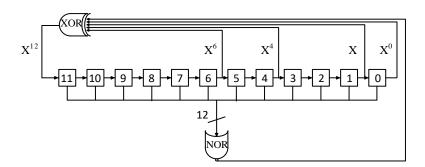

| 14.  | Cyclic  | Redundancy Check (CRC)                                | 209 |

| 14.1.     | Introduction                                                            | 209 |

|-----------|-------------------------------------------------------------------------|-----|

| 14.2.     | CRC Key Features                                                        | 209 |

| 14.3.     | CRC Functional Description                                              | 209 |

| 14.3.1.   | CRC Block Diagram                                                       | 209 |

| 14.4.     | CRC Register                                                            | 210 |

| 14.4.1.   | Data register (CRC_DR)                                                  | 210 |

| 14.4.2.   | Independent Data Register (CRC_IDR)                                     | 210 |

| 14.4.3.   | Control Register (CRC_CR)                                               | 211 |

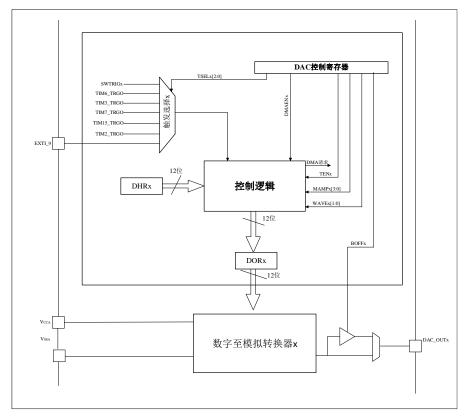

| l5. Digit | al/Analog Conversion (DAC)                                              | 212 |

| 15.1.     | DAC Introduction                                                        | 212 |

| 15.2.     | DAC Main Features                                                       | 212 |

| 15.3.     | DAC Functional Description                                              | 213 |

| 15.3.1.   | Using DAC channels                                                      | 213 |

| 15.3.2.   | Using the DAC Output Buffer                                             | 213 |

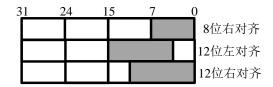

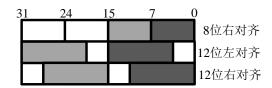

| 15.3.3.   | DAC Data Format                                                         | 213 |

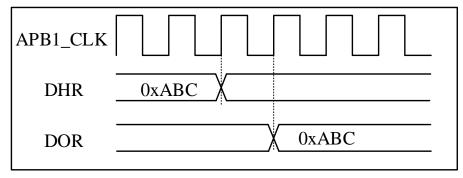

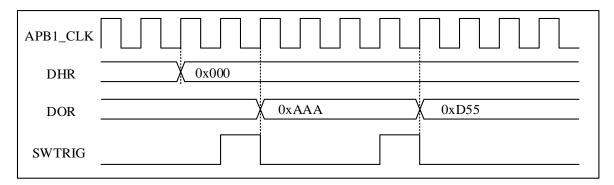

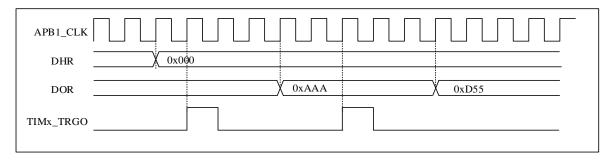

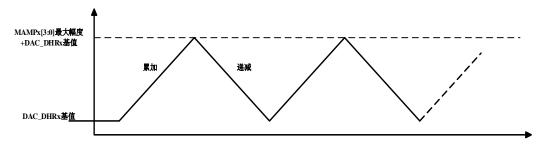

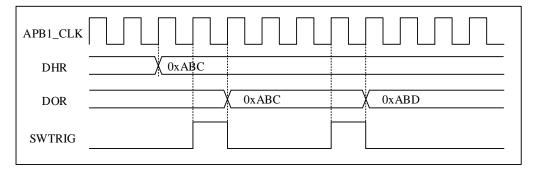

| 15.3.4.   | DAC conversion                                                          | 214 |

| 15.3.5.   | DAC Output Voltage                                                      | 215 |

| 15.3.6.   | Select DAC Trigger                                                      | 215 |

| 15.3.7.   | DMA function                                                            | 216 |

| 15.4.     | DAC Register                                                            | 223 |

| 15.4.1.   | DAC Control Register (DAC_CR)                                           | 223 |

| 15.4.2.   | DAC Software Trigger Register (DAC_SWTRIGR)                             | 228 |

| 15.4.3.   | 12-bit right-aligned data hold register for DAC channel 1 (DAC_DHR12R1) | 228 |

| 15.4.4.   | 12-bit left-aligned data hold register for DAC channel 1 (DAC_DHR12L1)  | 229 |

| 15.4.5.   | 8-bit right-aligned data hold register for DAC channel 1 (DAC_DHR8R1)   | 229 |

| 15.4.6.   | 12-bit right-aligned data hold register for DAC channel 2 (DAC_DHR12R2) | 230 |

| 15.4.7.   | 12-bit left-aligned data hold register for DAC channel 2 (DAC_DHR12L2)  | 230 |

| 15.4.8.   | 8-bit right-aligned data hold register for DAC channel 2 (DAC_DHR8R2)   | 231 |

| 15.4.9.   | 12-bit right-aligned data hold register for dual DACs (DAC_DHR12RD)     | 231 |

| 15.4.10   | . 12-bit left-aligned data hold register for dual DACs (DAC_DHR12LD)    | 232 |

| 15.4.11   | . 8-bit right-aligned data hold register for dual DACs (DAC_DHR8RD)     | 232 |

| 15.4.12   | DAC channel 1 data output register (DAC_DOR1)                           | 233 |

| 15.4.13   | DAC channel 2 data output register (DAC_DOR2)                           | 233 |

| 15.4.14   | DAC Status Register (DAC_SR)                                            | 234 |

| l6. Anal  | og/Digital Conversion (ADC)                                             | 235 |

| 16.1.     | Introduction                                                            | 235 |

| 16.2.     | ADC Main Characteristics                                                | 235 |

| 16.3.     | ADC Functional Description                                              | 236 |

| 16.3.1.   | ADC Block Diagram                                                       | 236 |

| 1632      | Calibrations                                                            | 236 |

| 16.3.   | .3. ADC Switch Control                                            | 237     |

|---------|-------------------------------------------------------------------|---------|

| 16.3.   | .4. ADC Clock                                                     | 237     |

| 16.3.   | .5. Channel Selection                                             | 237     |

| 16.3.   | .6. Programmable sampling time                                    | 238     |

| 16.3.   | .7. Configurable resolution                                       | 238     |

| 16.3.   | .8. Single conversion mode                                        | 239     |

| 16.3.   | .9. Continuous Conversion Mode                                    | 239     |

| 16.3.   | .10. Scanning mode                                                | 239     |

| 16.3.   | .11. intermittent switching mode                                  | 240     |

| 16.3.   | .12. Injection channel management                                 | 241     |

| 16.3.   | .13. Stopping conversions in progress (ADSTP)                     | 242     |

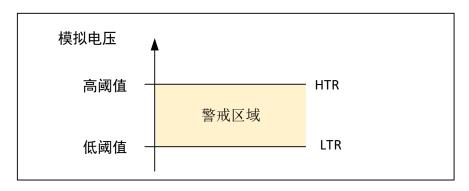

| 16.4.   | Analog Watchdog                                                   | 242     |

| 16.5.   | Externally Triggered Conversion                                   | 243     |

| 16.6.   | Data alignment                                                    | 244     |

| 16.7.   | Data overload                                                     | 244     |

| 16.8.   | DMA request                                                       | 244     |

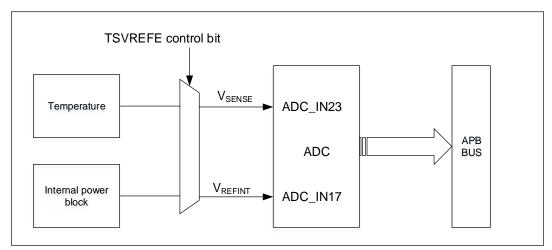

| 16.9.   | Temperature sensor and internal reference voltage                 | 244     |

| 16.10.  | ADC Interrupt                                                     | 246     |

| 16.11.  | ADC Registers                                                     |         |

| 16.11   | 1.1. ADC Status Register (ADC_SR)                                 | 246     |

| 16.11   | 1.2. ADC Control Register 1 (ADC_CR1)                             | 247     |

| 16.11   | 1.3. ADC Control Register (ADC_CR2)                               | 251     |

| 16.11   |                                                                   |         |

| 16.11   |                                                                   |         |

| 16.11   | 1.6. ADC Sample Time Register 3 (ADC_SMPR3)                       | 255     |

| 16.11   | 1.7. ADC injection channel data offset register x (ADC_JOFRx) (x- | =14)256 |

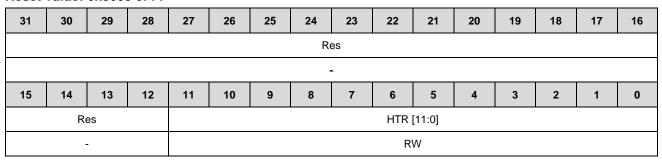

| 16.11   | 1.8. ADC Watchdog High Threshold Register (ADC_HTR)               | 256     |

| 16.11   | 1.9. ADC Watchdog Low Threshold Register (ADC_LTR)                | 257     |

| 16.11   |                                                                   |         |

| 16.11   | 1.11. ADC Rule Sequence Register 2 (ADC_SQR2)                     | 258     |

| 16.11   |                                                                   |         |

| 16.11   | 1.13. ADC Injection Sequence Register (ADC_JSQR)                  | 260     |

| 16.11   | , , , , , , , , , , , , , , , , , , , ,                           |         |

| 16.11   | 9 ( – ,                                                           |         |

|         | 1.16. ADC Calibration Configuration and Status Register (ADC_CC   |         |

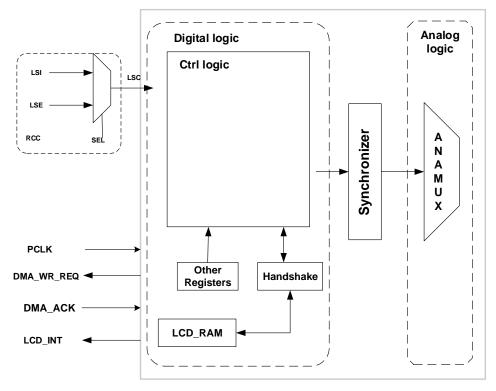

| 17. Lic | quid Crystal Controller (LCD)                                     |         |

| 17.1.   | Introduction                                                      |         |

| 17.2.   | LCD Main Characteristics                                          |         |

| 17.3.   | LCD Block Diagram                                                 | 266     |

| 17.4.   | LCD clock                                                         | 266     |

| 17.5.   | LCD Driver Waveforms                            | 266 |

|---------|-------------------------------------------------|-----|

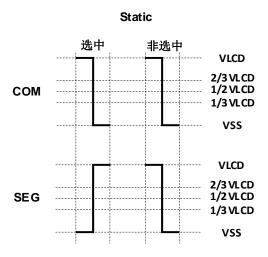

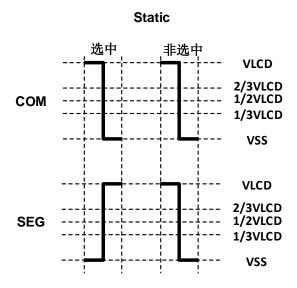

| 17.5.1  | Static drive waveform                           | 267 |

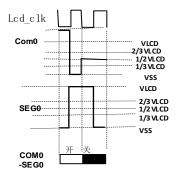

| 17.5.2  | . 1/2DUTY 1/2BIAS Drive Waveforms               | 267 |

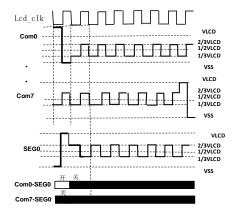

| 17.5.3  | . 1/8DUTY 1/3BIAS Drive Waveforms               | 267 |

| 17.6.   | LCD BIAS Generation Circuit                     | 268 |

| 17.6.1  | . Internal Resistance Mode                      | 268 |

| 17.6.2  | External Resistance Mode                        | 269 |

| 17.7.   | DMA                                             | 269 |

| 17.8.   | Disruptions                                     | 269 |

| 17.9.   | LCD display mode                                | 270 |

| 17.9.1  | . LCD display mode 1 (MODE = 1)                 | 270 |

| 17.9.2  | . LCD display mode 0 (MODE = 0)                 | 272 |

| 17.10.  | LCD Register                                    | 275 |

| 17.10.  | 1. Configuration Register 0 (LCD_CR0)           | 275 |

| 17.10.  | 2. Configuration Register 1 (LCD_CR1)           | 276 |

| 17.10.  | 3. Interrupt Clear Register (LCD_INTCLR)        | 277 |

| 17.10.  | 4. Output configuration register (LCD_POEN0)    | 277 |

| 17.10.  | 5. Output Configuration Register 1 (LCD_POEN1)  | 278 |

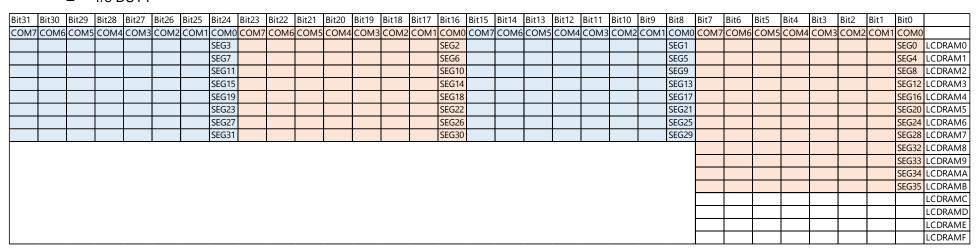

| 17.10.  | 6. LCD_RAM0~7                                   | 280 |

| 17.10.  | 7. LCD_RAM8~F                                   | 280 |

| 18. Con | nparator (COMP)                                 | 281 |

| 18.1.   | Introduction                                    | 281 |

| 18.2.   | COMP Key Features                               | 281 |

| 18.3.   | COMP Functional Description                     | 282 |

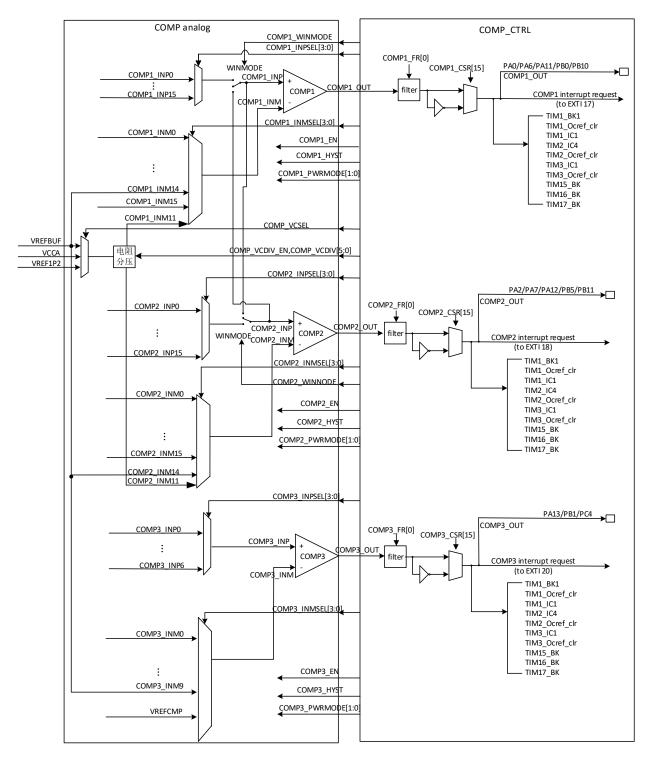

| 18.3.1  | COMP Block Diagram                              | 282 |

| 18.3.2  | . COMP pin and internal signals                 | 283 |

| 18.3.3  | COMP Reset and Clock                            | 283 |

| 18.3.4  | . Window comparator                             | 283 |

| 18.3.5  | •                                               |     |

| 18.3.6  | Power consumption mode                          | 284 |

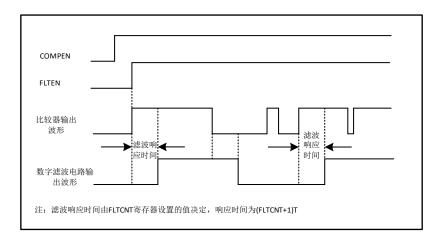

| 18.3.7  | Comparator Filter                               | 284 |

| 18.3.8  | COMP interrupt                                  | 285 |

| 18.4.   | COMP register                                   | 285 |

| 18.4.1  | . COMP1 Control and Status Register (COMP1_CSR) | 285 |

| 18.4.2  | . COMP1 Filter Register (COMP1_FR)              | 287 |

| 18.4.3  | . COMP2 Control and Status Register (COMP2_CSR) | 288 |

| 18.4.4  | . COMP2 Filter Register (COMP2_FR)              | 290 |

| 18.4.5  | <b>5</b> ( – ,                                  |     |

| 18.4.6  | · - /                                           |     |

| 19. Ope | rational amplifiers (OPA)                       | 294 |

|    | 19.1.   | OPA Introduction                                   | 294 |

|----|---------|----------------------------------------------------|-----|

|    | 19.2.   | OPA Main Characteristics                           | 294 |

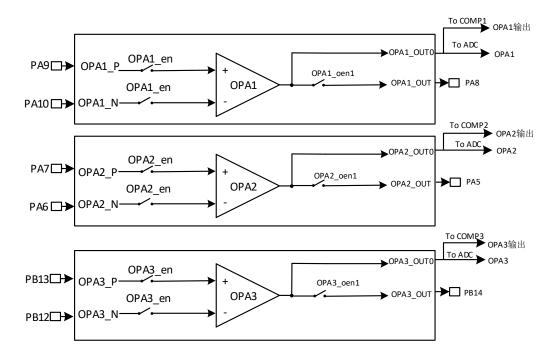

|    | 19.3.   | OPA Functional Description                         | 294 |

|    | 19.3.1. | OPA Block Diagram                                  | 294 |

|    | 19.4.   | OPA Register                                       | 295 |

|    | 19.4.1. | OPA output enable register (OPA_CR0)               | 295 |

|    | 19.4.2. | OPA Control Register (OPA_CR1)                     | 295 |

| 2( | ). Hard | dware divider (DIV)                                | 296 |

|    | 20.1.   | DIV Introduction                                   | 296 |

|    | 20.2.   | DIV Key Features                                   | 296 |

|    | 20.3.   | DIV Function Description                           | 296 |

|    | 20.3.1. | DIV operation flow                                 | 296 |

|    | 20.4.   | DIV register                                       | 297 |

|    | 20.4.1. | DIV Divisor Register (DIV_DEND)                    | 297 |

|    | 20.4.2. | DIV Divisor Register (DIV_SOR)                     | 297 |

|    | 20.4.3. | DIV Business Register (DIV_QUOT)                   | 297 |

|    | 20.4.4. | DIV Remainder Register (DIV_REMD)                  | 298 |

|    | 20.4.5. | DIV symbol register (DIV_SIGN)                     | 298 |

|    | 20.4.6. | DIV Status Register (DIV_STAT)                     | 298 |

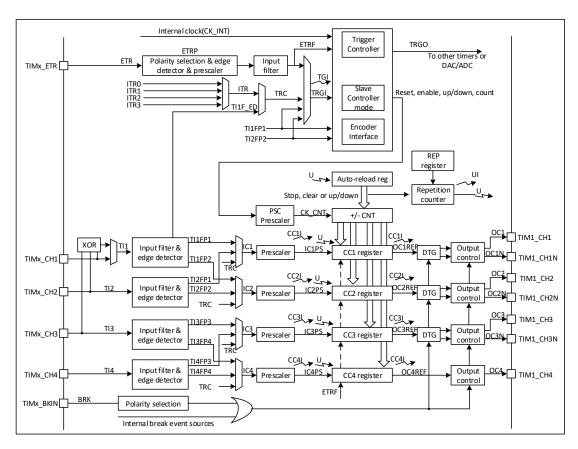

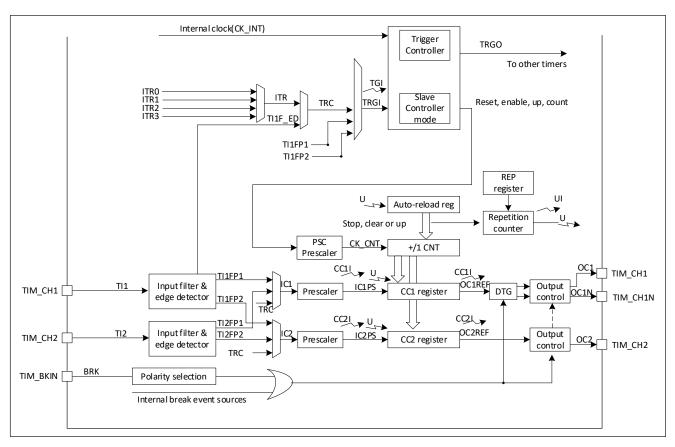

| 21 | I. Adv  | anced Control Timer (TIM1)                         | 300 |

|    | 21.1.   | TIM1 Introduction                                  | 300 |

|    | 21.2.   | TIM1 Main Features                                 | 300 |

|    | 21.3.   | TIM1 Function Description                          | 301 |

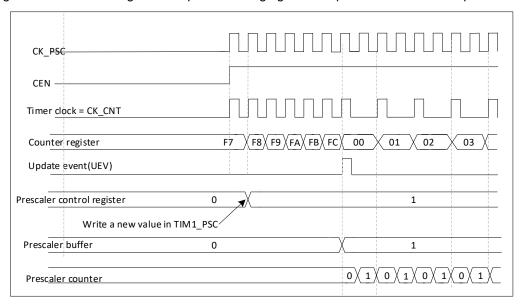

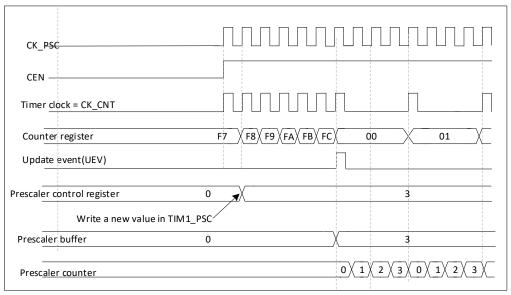

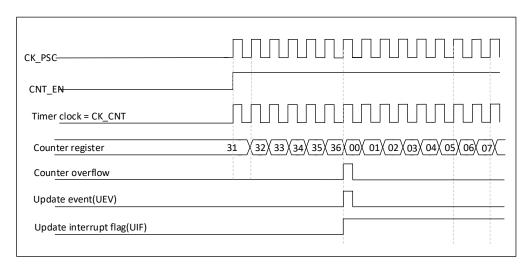

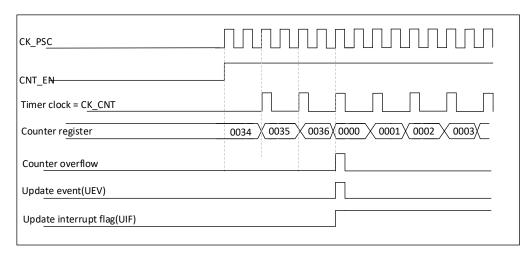

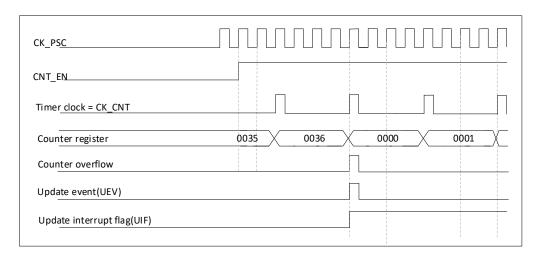

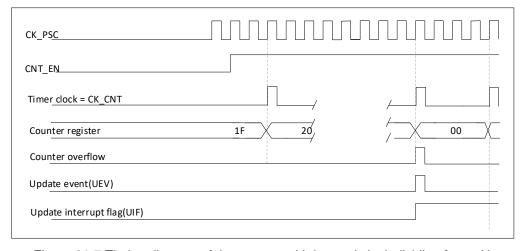

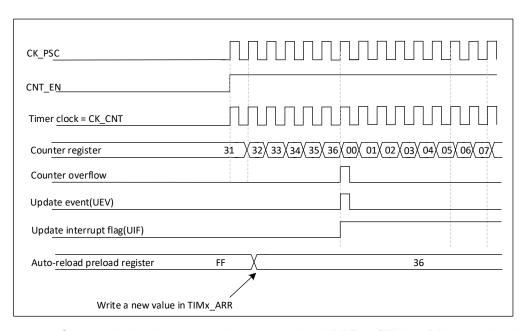

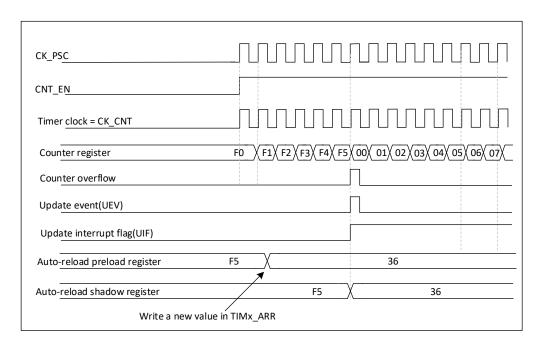

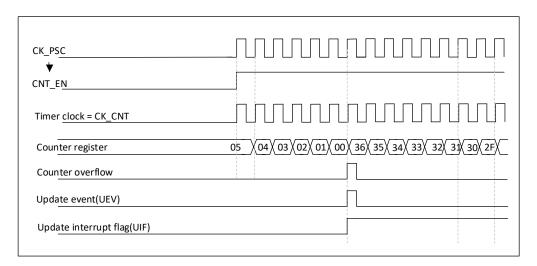

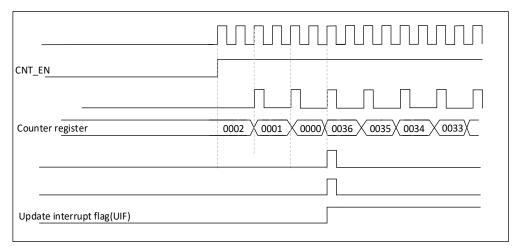

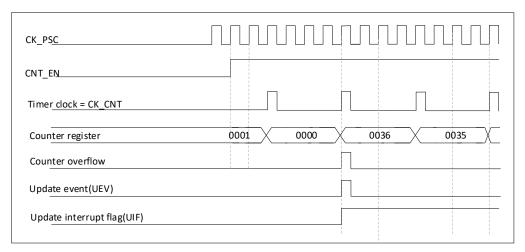

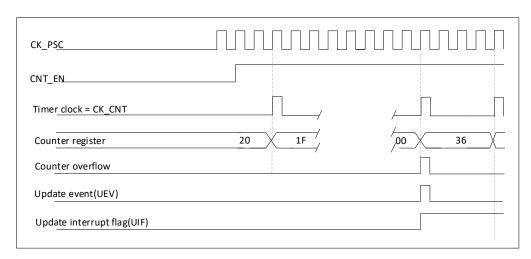

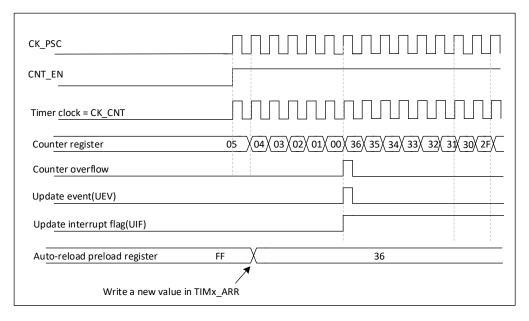

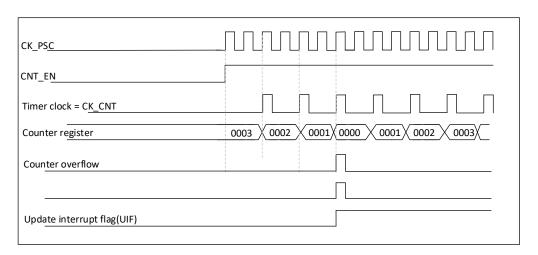

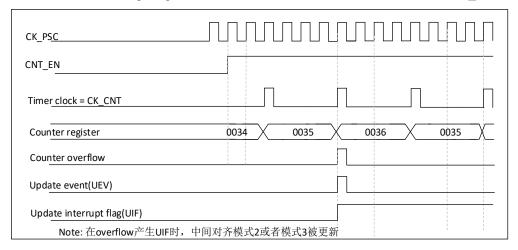

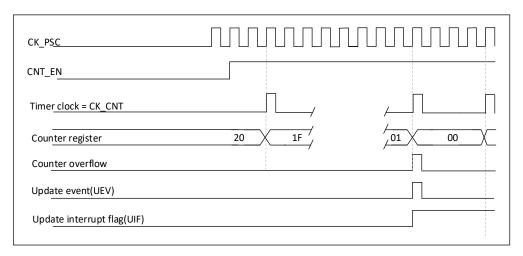

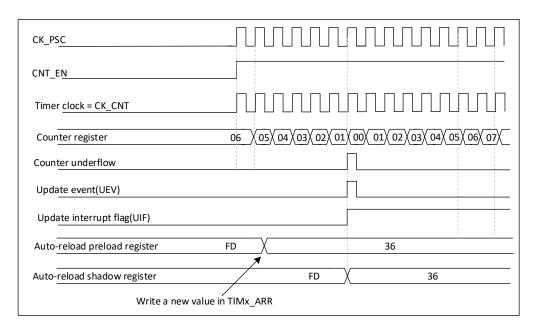

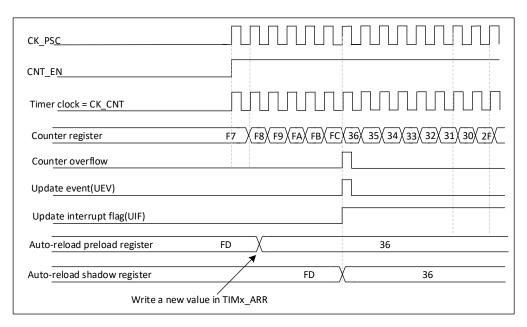

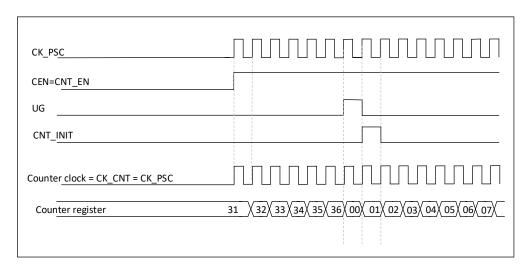

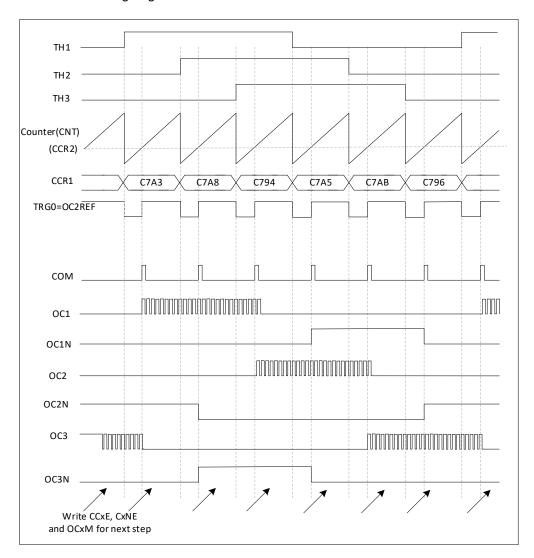

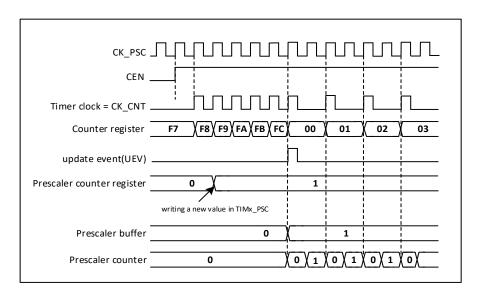

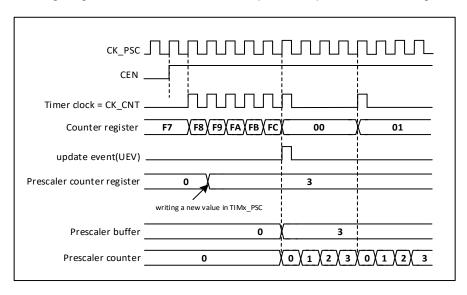

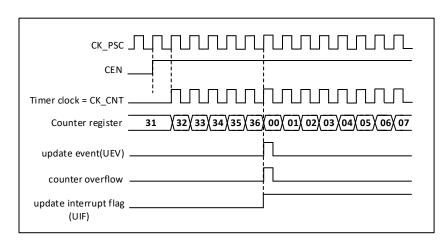

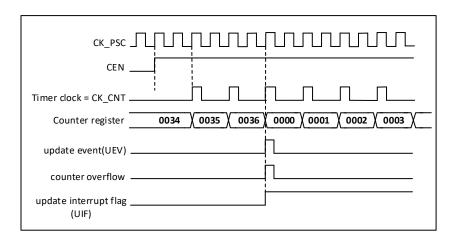

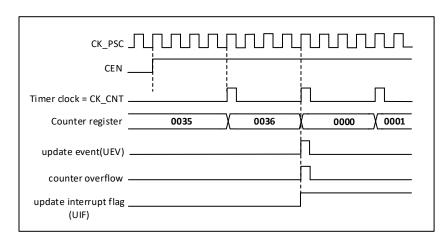

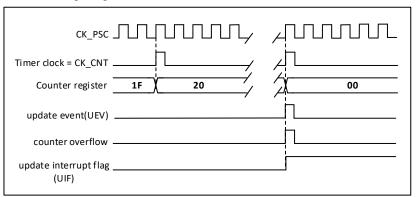

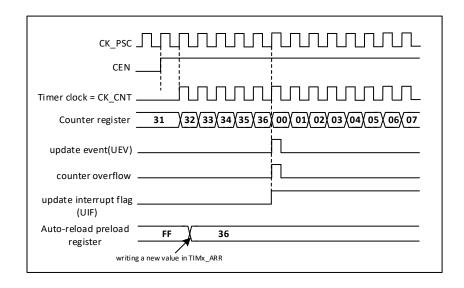

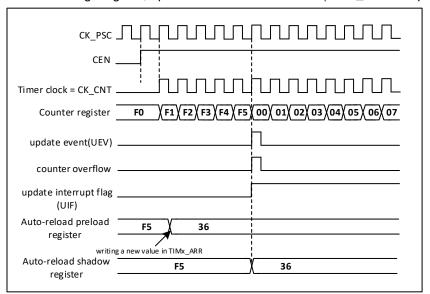

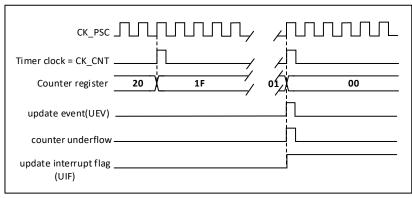

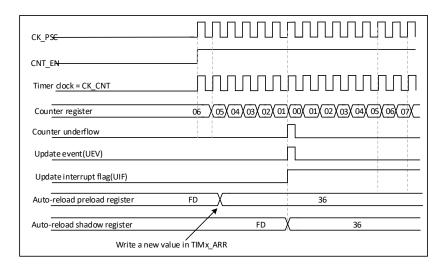

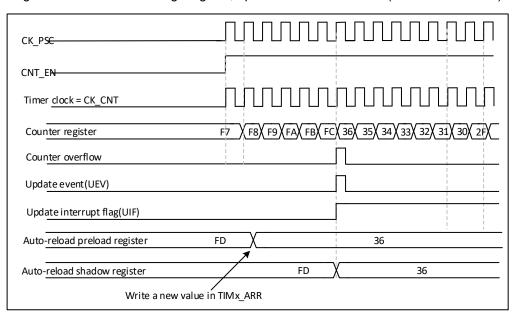

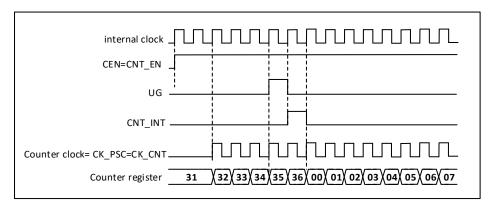

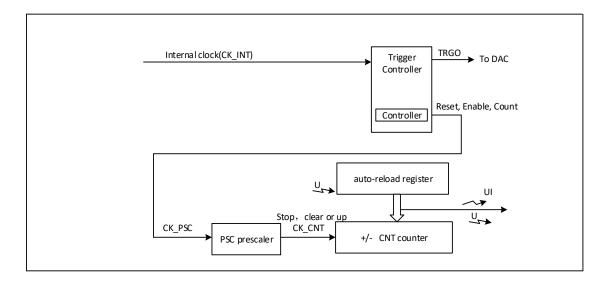

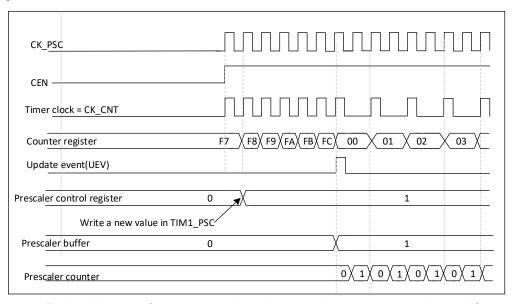

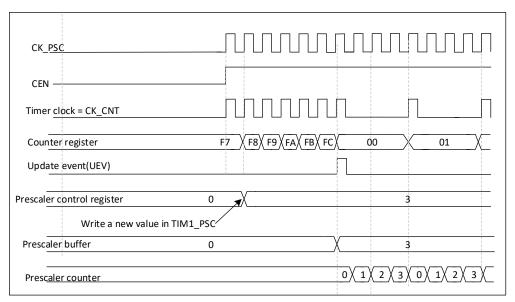

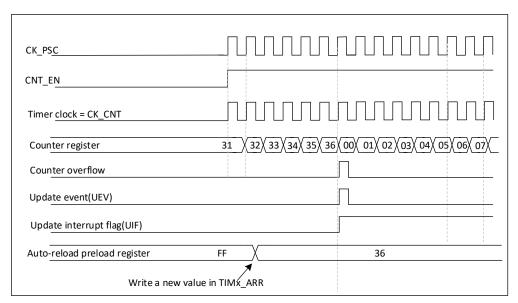

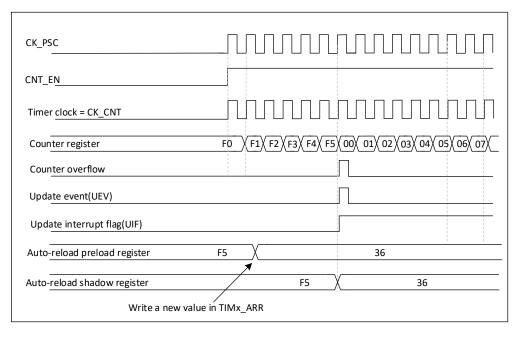

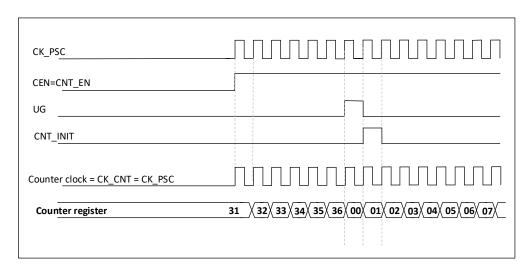

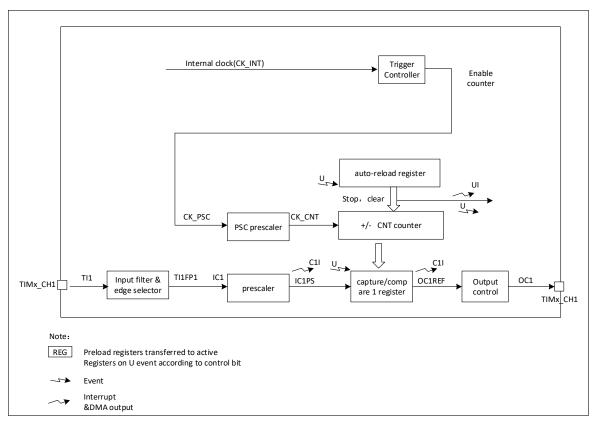

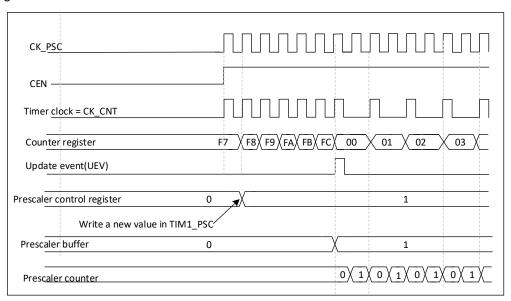

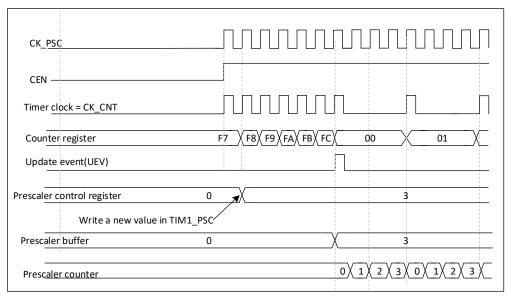

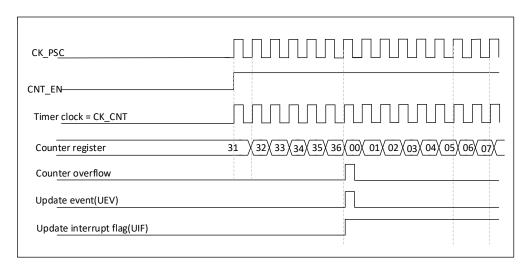

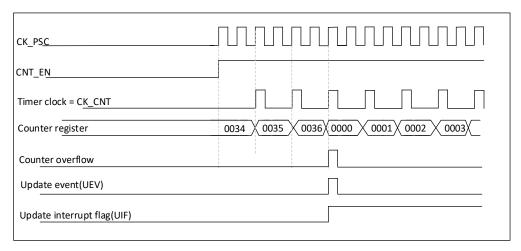

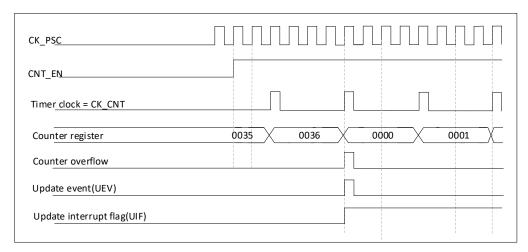

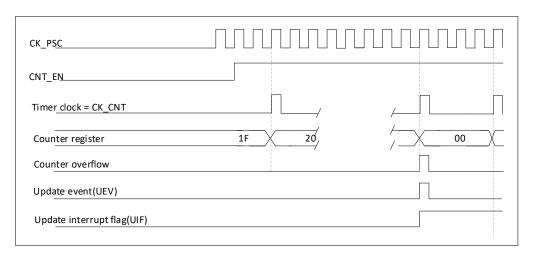

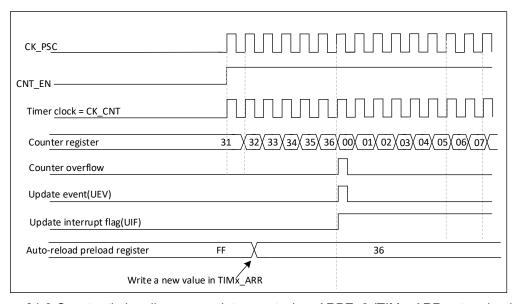

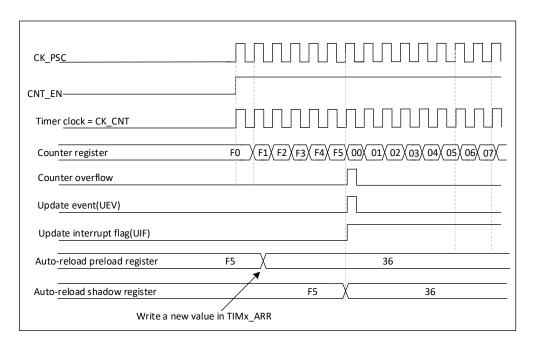

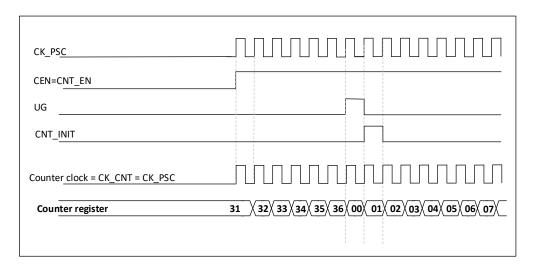

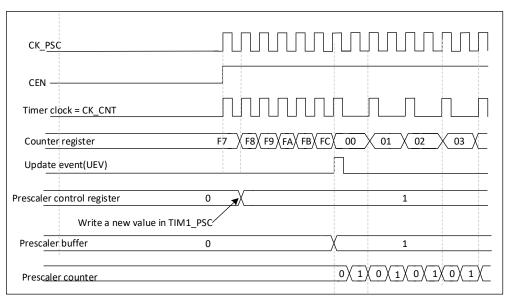

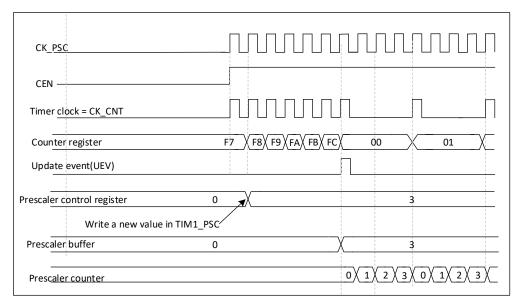

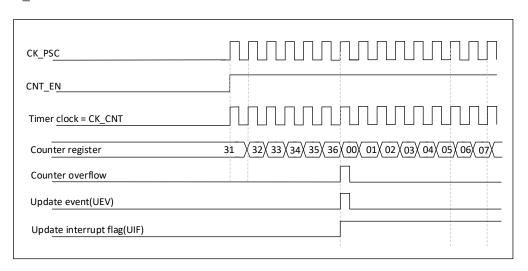

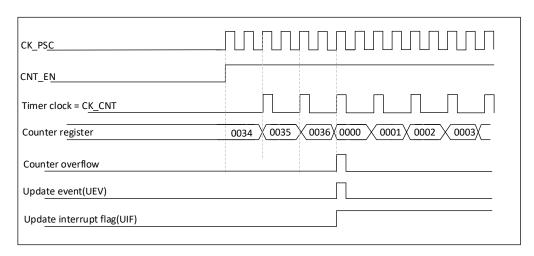

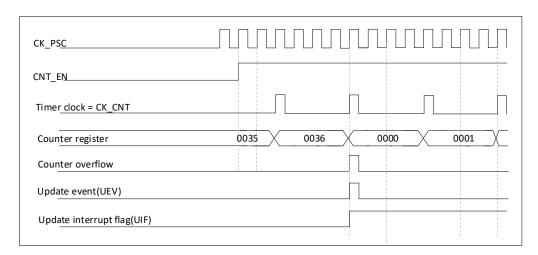

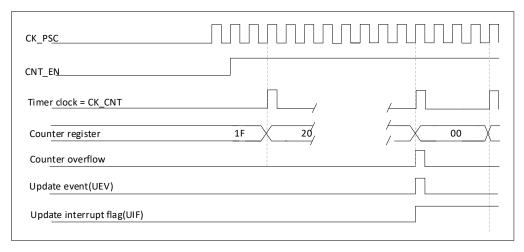

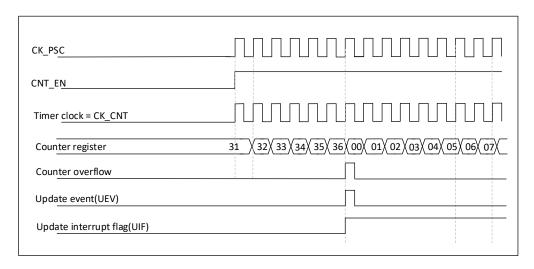

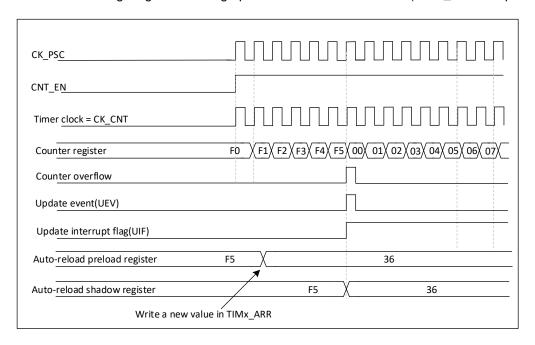

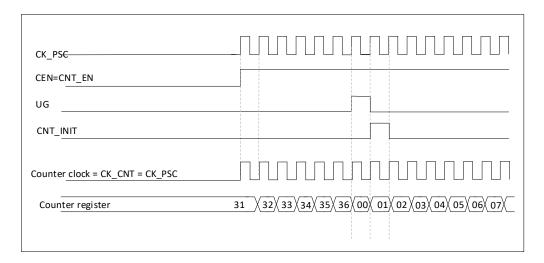

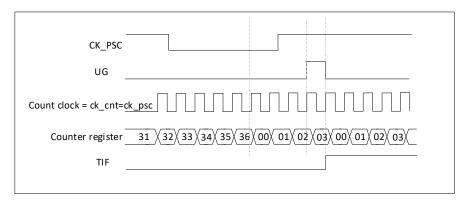

|    | 21.3.1. | Time base unit (in computing)                      | 301 |

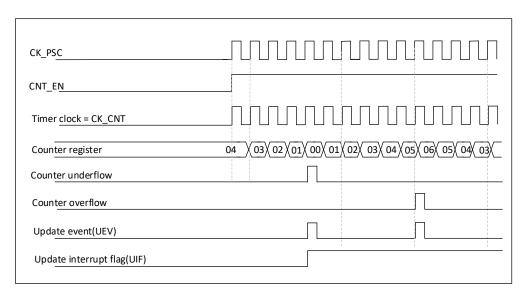

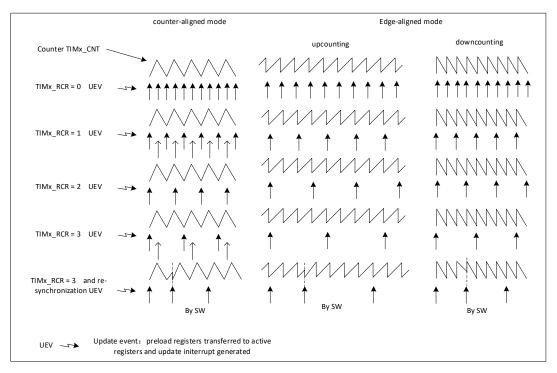

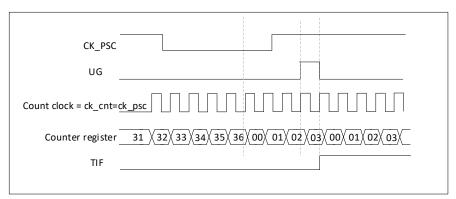

|    | 21.3.2. | Counter Mode                                       | 302 |

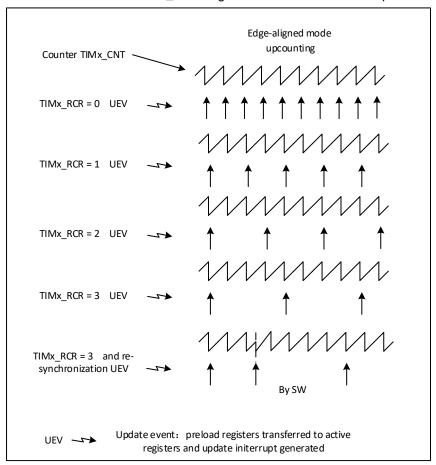

|    | 21.3.3. | Repetition counter                                 | 311 |

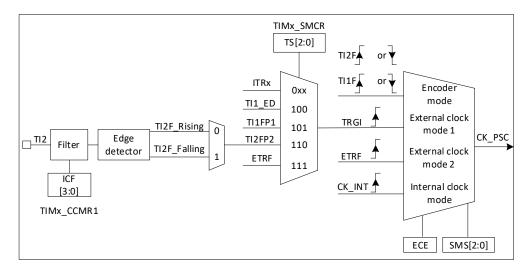

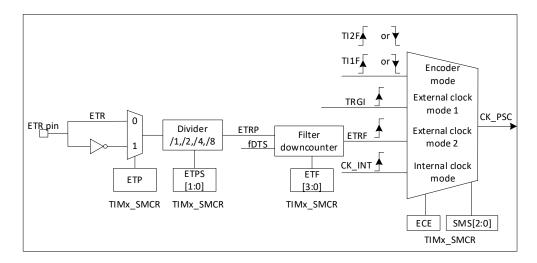

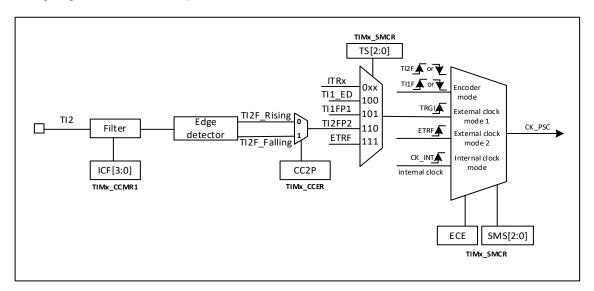

|    | 21.3.4. | Clock source                                       | 312 |

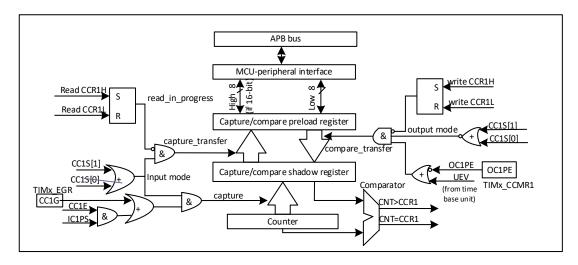

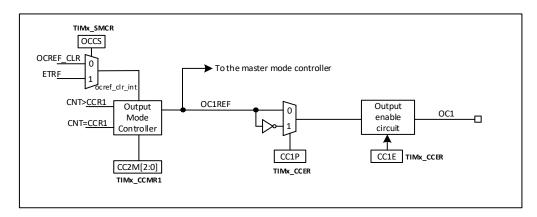

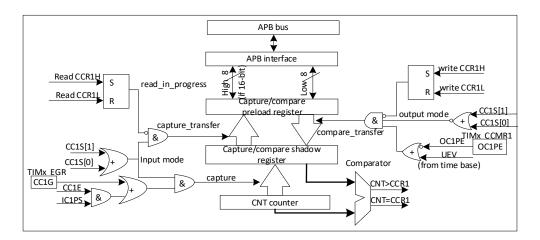

|    | 21.3.5. | Capture/Compare Channel                            | 314 |

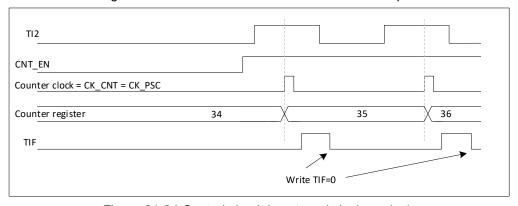

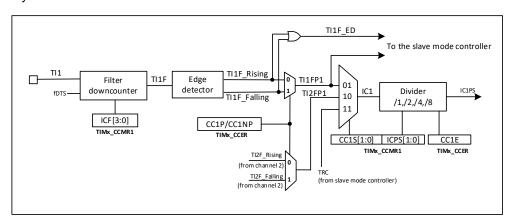

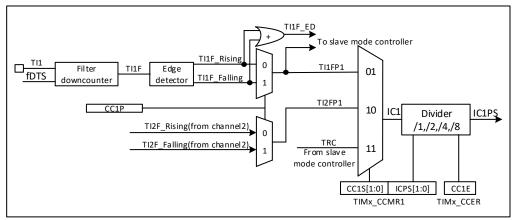

|    | 21.3.6. | Input Capture Mode                                 | 316 |

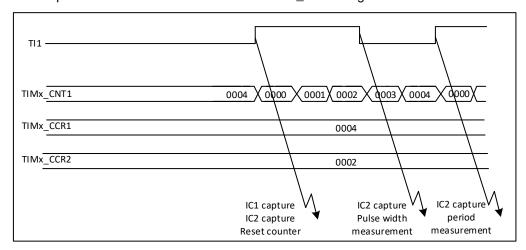

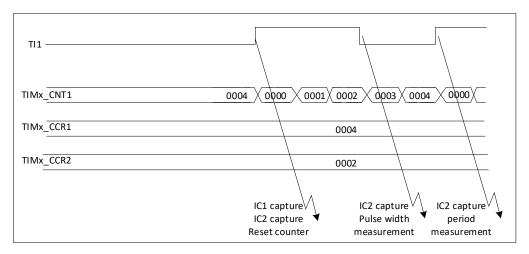

|    | 21.3.7. | PWM Input Mode                                     | 317 |

|    | 21.3.8. | Forced Output Mode                                 | 318 |

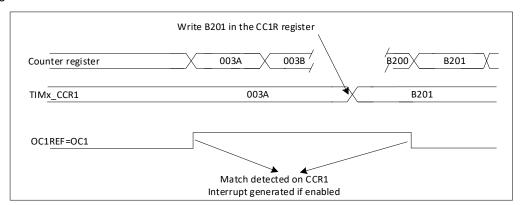

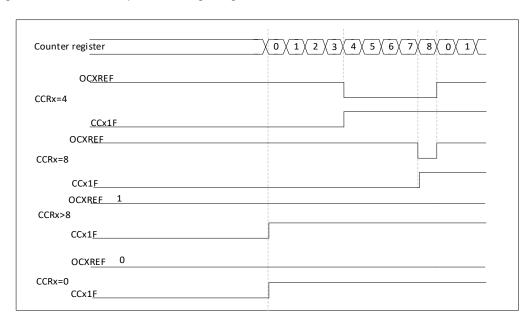

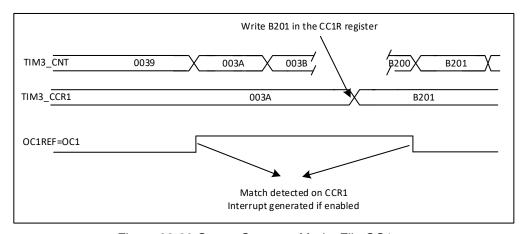

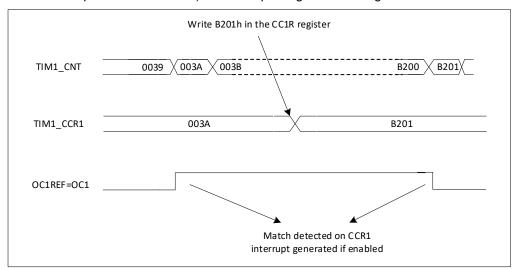

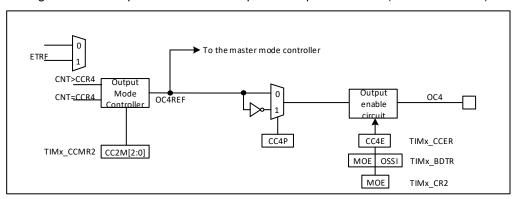

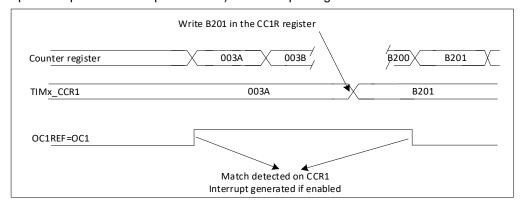

|    | 21.3.9. | Output Comparison Mode                             | 318 |

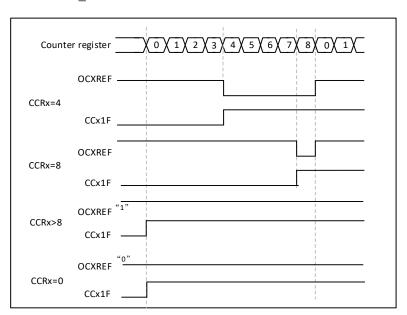

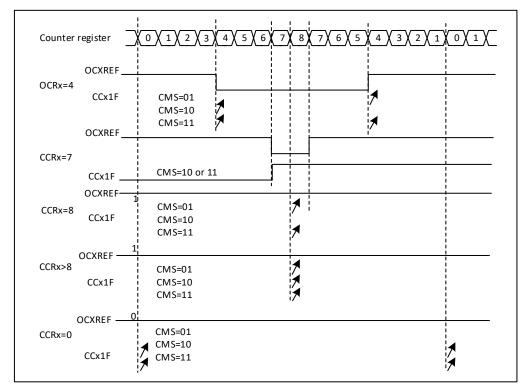

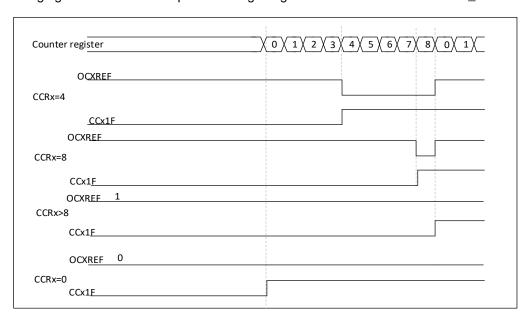

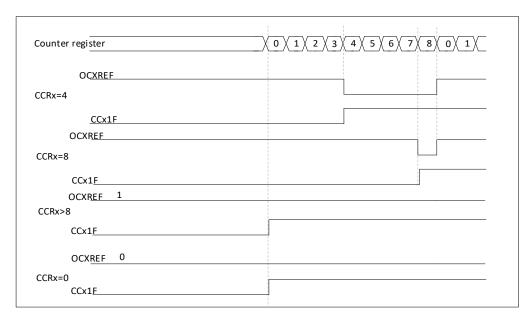

|    | 21.3.10 | 0. PWM mode                                        | 319 |

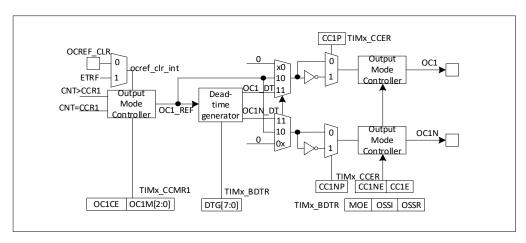

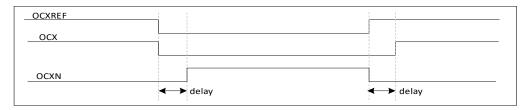

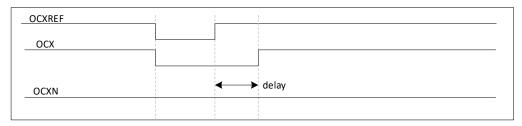

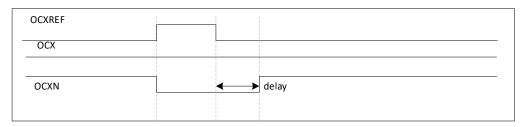

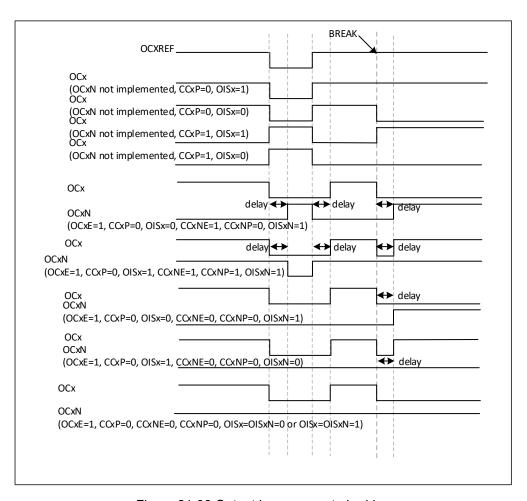

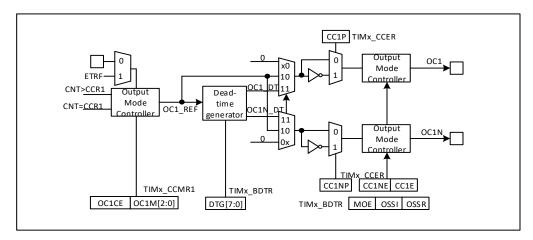

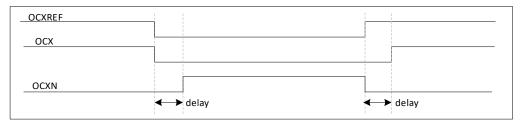

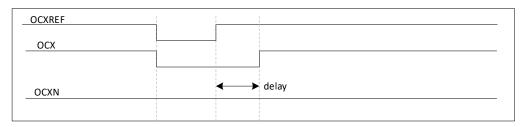

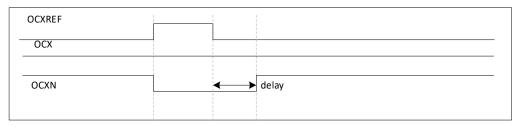

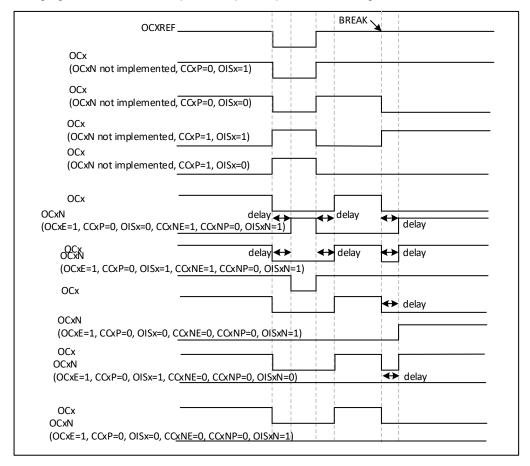

|    | 21.3.1  | Complementary outputs and deadband insertion       | 322 |

|    | 21.3.12 | 2. Using the brake function                        | 323 |

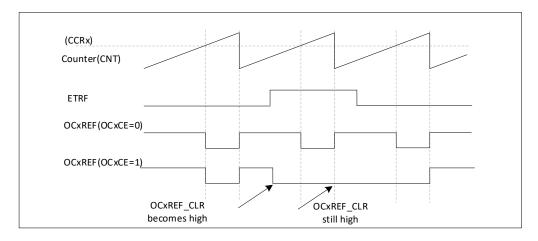

|    | 21.3.13 | 3. Clearing the OCxREF signal on an external event | 325 |

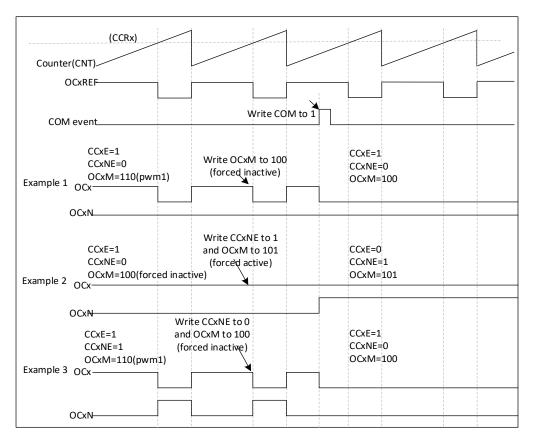

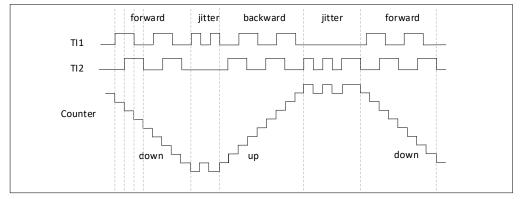

|    | 21.3.14 | 4. Six-step PWM generation                         | 326 |

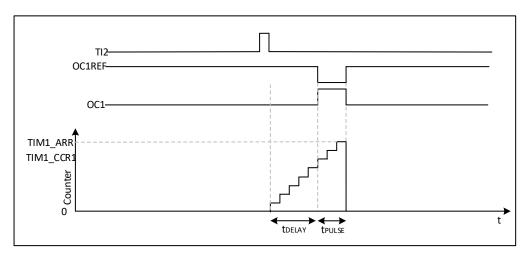

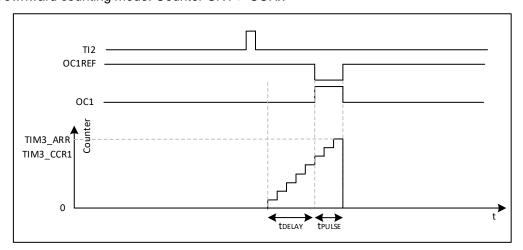

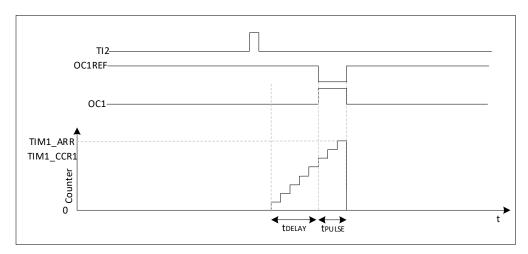

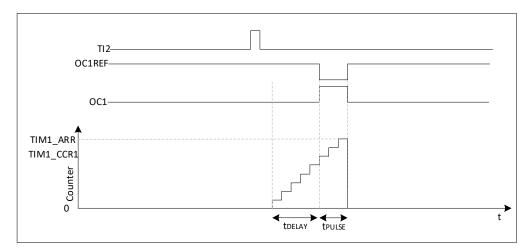

|    | 21.3.1  | 5. Single Pulse Mode                               | 327 |

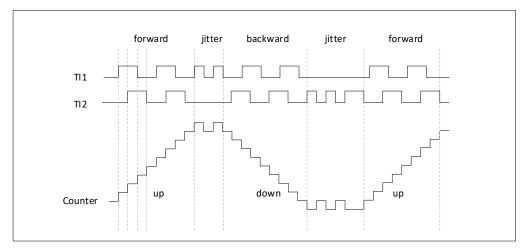

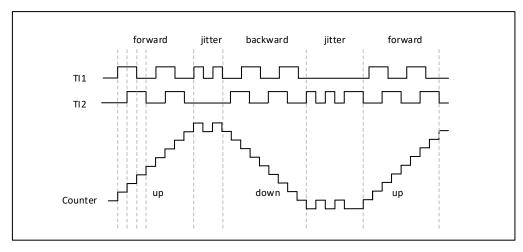

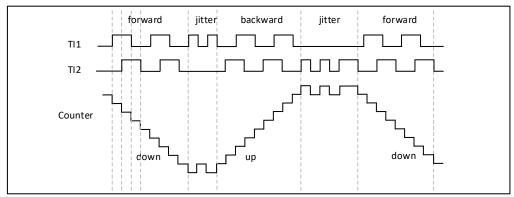

|    | 21.3.10 | 6. Encoder Interface Mode                          | 329 |

|    | 21.3.17 | 7. Timer input heterodyne function                 | 331 |

| 21.3.18. | Interfacing with Hall Sensors                    | 331 |

|----------|--------------------------------------------------|-----|

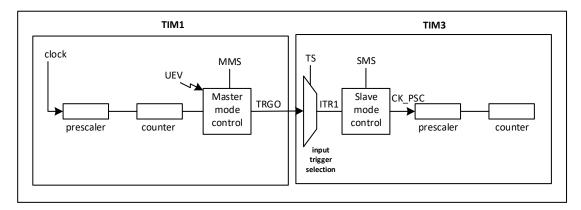

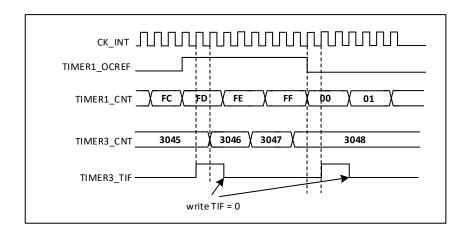

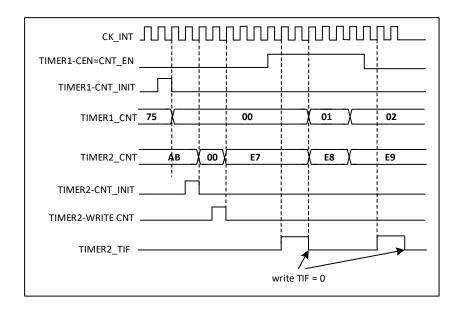

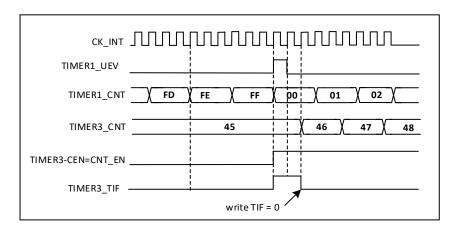

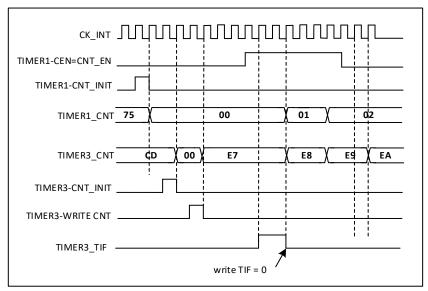

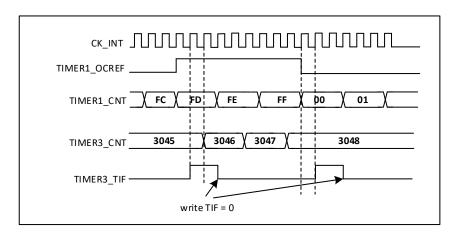

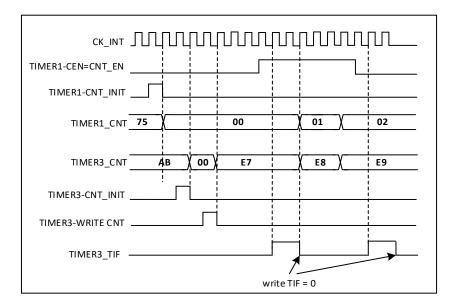

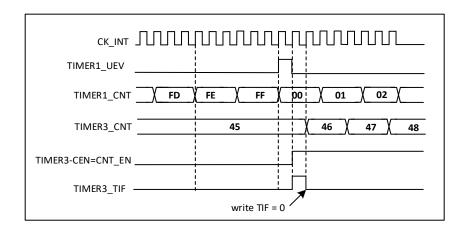

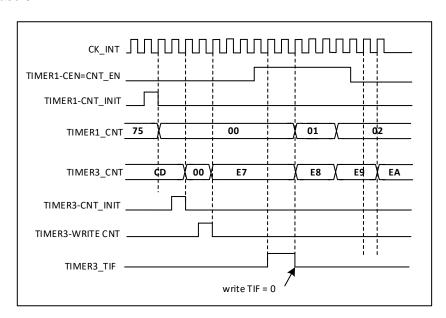

| 21.3.19. | Timer and external trigger synchronization       | 332 |

| 21.3.20. | Timer synchronization                            | 335 |

| 21.3.21. | Debug mode                                       | 335 |

| 21.4.    | FIM1 Register Description                        | 335 |

| 21.4.1.  | TIM1 Control Register 1 (TIM1_CR1)               | 335 |

| 21.4.2.  | TIM1 Control Register 2 (TIM1_CR2)               | 338 |

| 21.4.3.  | TIM1 Slave Mode Control Register (TIM1_SMCR)     | 340 |

| 21.4.4.  | TIM1 DMA/Interrupt Enable Register (TIM1_DIER)   | 343 |

| 21.4.5.  | TIM1 status register (TIM1_SR)                   | 345 |

| 21.4.6.  | TIM1 Event Generation Register (TIM1_EGR)        | 348 |

| 21.4.7.  | TIM1 Capture/Compare Mode Register 1 (TIM1_CMR1) | 350 |

| 21.4.8.  | TIM1 Capture/Compare Mode Register 2 (TIM1_CMR2) | 354 |

| 21.4.9.  | TIM1 Capture/Compare Enable Register (TIM1_CCER) | 356 |

| 21.4.10. | TIM1 Counter (TIM1_CNT)                          | 360 |

| 21.4.11. | TIM1 prescaler (TIM1_PSC)                        | 360 |

| 21.4.12. | TIM1 Auto-Reload Register (TIM1_ARR)             | 361 |

| 21.4.13. | TIM1 Repeat Counter Register (TIM1_RCR)          | 361 |

| 21.4.14. | TIM1 Capture/Compare Register 1 (TIM1_CCR1)      | 362 |

| 21.4.15. | TIM1 Capture/Compare Register 2 (TIM1_CCR2)      | 363 |

| 21.4.16. | TIM1 Capture/Compare Register 3 (TIM1_CCR3)      | 364 |

| 21.4.17. | TIM1 Capture/Compare Register 4 (TIM1_CCR4)      | 364 |

| 21.4.18. | TIM1 Brake and Deadband Register (TIM1_BDTR)     | 365 |

| 21.4.19. | TIM1 DMA Control Register (TIM1_DCR)             | 368 |

| 21.4.20. | TIM1 continuous mode DMA address (TIM1_DMAR)     | 369 |

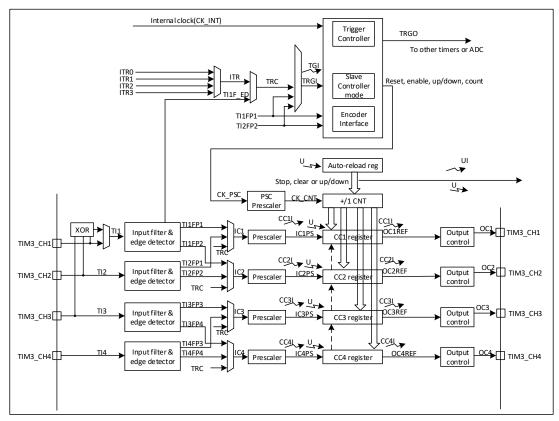

| 22. Gene | ral purpose timer (TIM2/3)                       | 370 |

| 22.1. I  | ntroduction to TIM2/TIM3                         | 370 |

| 22.2.    | 「IM2/3 Main Features                             | 370 |

| 22.3.    | FIM2/3 Functional Description                    | 371 |

| 22.3.1.  | time base unit (in computing)                    | 371 |

| 22.3.2.  | Counter Mode                                     |     |

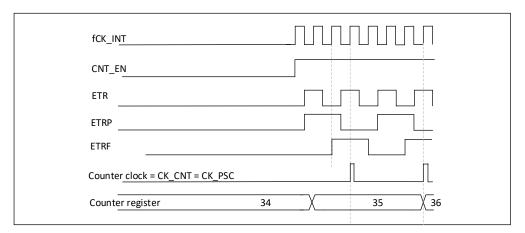

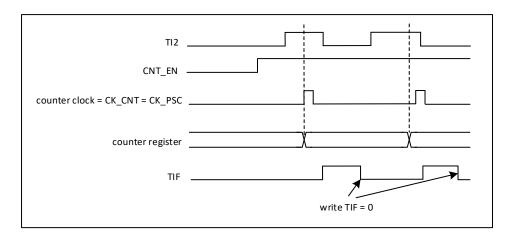

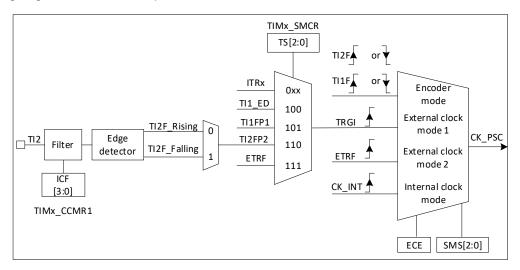

| 22.3.3.  | Clock source                                     | 380 |

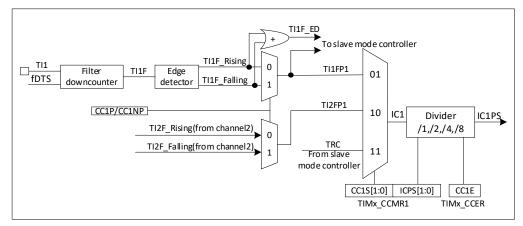

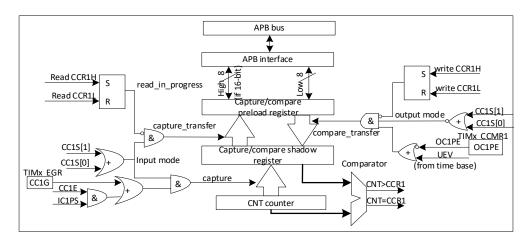

| 22.3.4.  | Capture/Compare Channel                          | 382 |

| 22.3.5.  | Input Capture Mode                               | 383 |

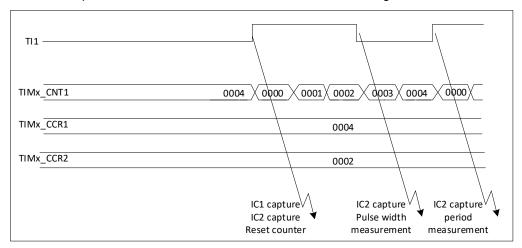

| 22.3.6.  | PWM Input Mode                                   | 384 |

| 22.3.7.  | Forced Output Mode                               | 385 |

| 22.3.8.  | Output Comparison Mode                           |     |

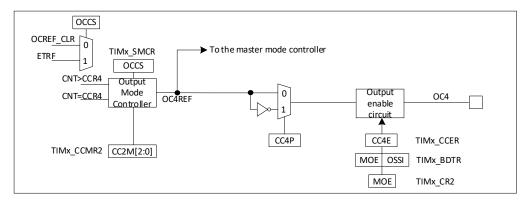

| 22.3.9.  | PWM mode                                         | 386 |

| 22.3.10. | Single Pulse Mode                                | 389 |

| 22.3.11. | Encoder Interface Mode                           | 390 |

| 22    | 2.3.12. | Timer input heterodyne function                           | 392 |

|-------|---------|-----------------------------------------------------------|-----|

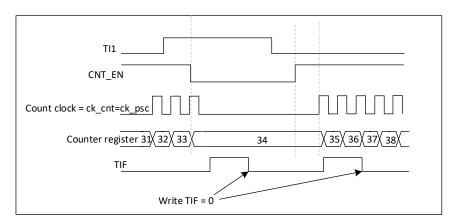

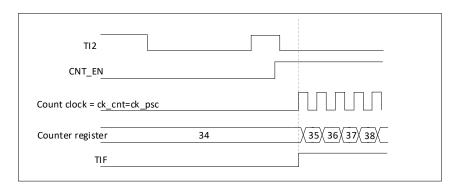

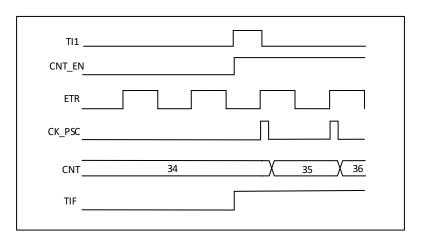

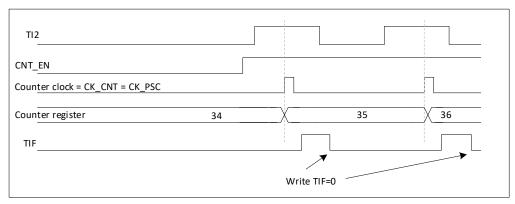

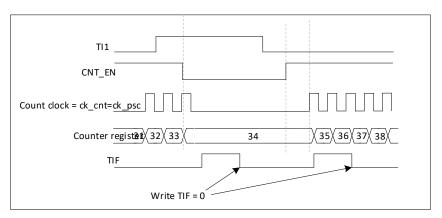

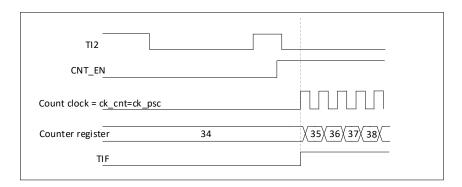

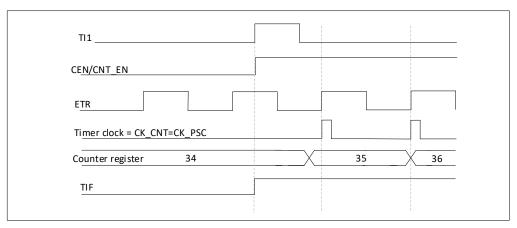

| 22    | 2.3.13. | Synchronization of timers and external triggers           | 392 |

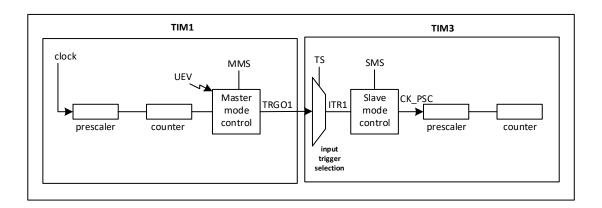

| 22    | 2.3.14. | Timer synchronization                                     | 395 |

| 22    | 2.3.15. | Debug mode                                                | 399 |

| 22.4. | . R     | egister description                                       | 399 |

| 22    | 2.4.1.  | TIM2/3 Control Register 1 (TIMx_CR1)                      | 400 |

| 22    | 2.4.2.  | TIM2/3 Control Register 2 (TIMx_CR2)                      | 402 |

| 22    | 2.4.3.  | TIM2/3 Slave Mode Control Register (TIMx_SMCR)            | 403 |

| 22    | 2.4.4.  | TIM2/3 DMA/Interrupt Enable Register (TIMx_DIER)          | 406 |

| 22    | 2.4.5.  | TIM2/3 status register (TIMx_SR)                          | 408 |

| 22    | 2.4.6.  | TIM2/3 Event Generation Register (TIMx_EGR)               | 410 |

| 22    | 2.4.7.  | TIM2/3 Capture/Compare Mode Register 1 (TIMx_CMR1)        | 412 |

| 22    | 2.4.8.  | TIM2/3 Capture/Compare Mode Register 2 (TIMx_CMR2)        | 416 |

| 22    | 2.4.9.  | TIM2/3 Capture/Compare Enable Register (TIMx_CCER)        | 418 |

| 22    | 2.4.10. | TIM2/3 counter (TIMx_CNT)                                 | 420 |

| 22    | 2.4.11. | TIM2/3 prescaler (TIMx_PSC)                               | 421 |

| 22    | 2.4.12. | TIM2/3 Automatic Reload Register (TIMx_ARR)               | 421 |

| 22    | 2.4.13. | TIM2/3 Capture/Compare Register 1 (TIMx_CCR1)             | 422 |

| 22    | 2.4.14. | TIM2/3 Capture/Compare Register 2 (TIMx_CCR2)             | 423 |

| 22    | 2.4.15. | TIM2/3 Capture/Compare Register 3 (TIMx_CCR3)             | 423 |

| 22    | 2.4.16. | TIM2/3 Capture/Compare Register 4 (TIMx_CCR4)             | 424 |

| 22    | 2.4.17. | TIM2/3 DMA Control Register (TIMx_DCR)                    | 425 |

| 22    | 2.4.18. | DMA address for TIM2/3 continuous mode (TIMx_DMAR)        | 426 |

| 23.   | Basic   | Timer (TIM6/7)                                            | 428 |

| 23.1. | . Ir    | ntroduction to TIM6 and TIM7                              | 428 |

| 23.2  | . K     | ey features of TIM6 and TIM7                              | 428 |

| 23.3. | . т     | IM6 and TIM7 Functional Description                       | 428 |

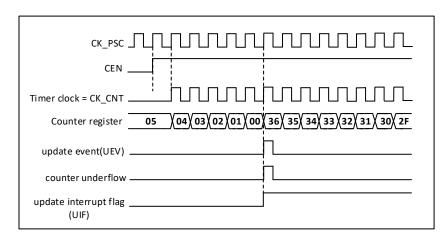

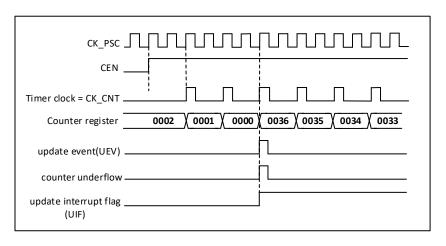

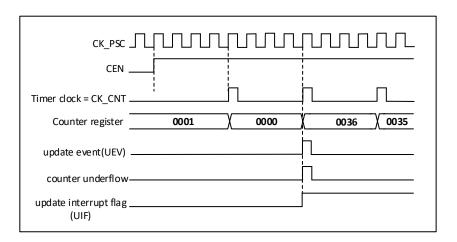

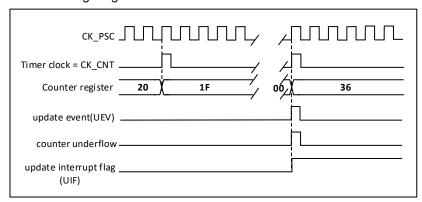

| 23    | 3.3.1.  | Time base unit (in computing)                             | 428 |

| 23    | 3.3.2.  | Clock source                                              | 433 |

| 23    | 3.3.3.  | Debug mode                                                | 433 |

| 23.4. | . т     | IM6 and TIM7 registers                                    | 434 |

| 23    | 3.4.1.  | TIM6 and TIM7 control register 1 (TIMx_CR1)               | 434 |

| 23    | 3.4.2.  | TIM6 and TIM7 Control Register 2 (TIMx_CR2)               | 435 |

| 23    | 3.4.3.  | TIM6 and TIM7 DMA/Interrupt Enable Registers (TIM14_DIER) | 436 |

| 23    | 3.4.4.  | TIM6 and TIM7 Status Registers (TIMx_SR)                  | 437 |

| 23    | 3.4.5.  | TIM6 and TIM7 Event Generation Registers (TIMx_EGR)       | 437 |

| 23    | 3.4.6.  | TIM6 and TIM7 counters (TIMx_CNT)                         | 438 |

| 23    | 3.4.7.  | TIM6 and TIM7 prescalers (TIMx_PSC)                       | 438 |

|       | 3.4.8.  | TIM6 and TIM7 Automatic Reload Registers (TIMx_ARR)       |     |

| 24.   | Gene    | al purpose timer (TIM14)                                  | 440 |

| 24.1.   | TIM14 Introduction                                   | 440 |

|---------|------------------------------------------------------|-----|

| 24.2.   | TIM14 main features                                  | 440 |

| 24.3.   | TIM14 Functional Description                         | 441 |

| 24.3.1  | . Time base unit (in computing)                      | 441 |

| 24.3.2  | Clock source                                         | 445 |

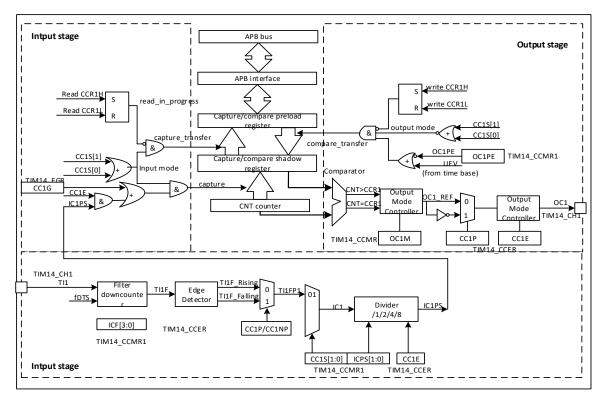

| 24.3.3  | . Capture/Compare Channel                            | 445 |

| 24.3.4  | . Input Capture Mode                                 | 446 |

| 24.3.5  | . Forced Output Mode                                 | 447 |

| 24.3.6  | Output Comparison Mode                               | 448 |

| 24.3.7  | PWM mode                                             | 448 |

| 24.3.8  | Single Pulse Mode                                    | 449 |

| 24.3.9  | . Timer synchronization                              | 450 |

| 24.3.1  | 0. Debug mode                                        | 451 |

| 24.4.   | TIM14 Register                                       | 451 |

| 24.4.1  | . TIM14 Control Register 1 (TIM14_CR1)               | 451 |

| 24.4.2  | . TIM14 DMA/Interrupt Enable Register (TIM14_DIER)   | 452 |

| 24.4.3  | TIM14 Status Register (TIM14_SR)                     | 453 |

| 24.4.4  | . TIM14 Event Generation Register (TIM14_EGR)        | 455 |

| 24.4.5  | . TIM14 Capture/Compare Mode Register 1 (TIM14_CMR1) | 455 |

| 24.4.6  | . TIM14 Capture/Compare Enable Register (TIM14_CCER) | 458 |

| 24.4.7  | . TIM14 Counter (TIM14_CNT)                          | 460 |

| 24.4.8  | . TIM14 Prescaler (TIM14_PSC)                        | 460 |

| 24.4.9  | . TIM14 Automatic Reload Register (TIM14_ARR)        | 461 |

| 24.4.1  | 0. TIM14 Capture/Compare Register 1 (TIM14_CCR1)     | 461 |

| 24.4.1  | 1. TIM14 option register (TIMx_OR)                   | 462 |

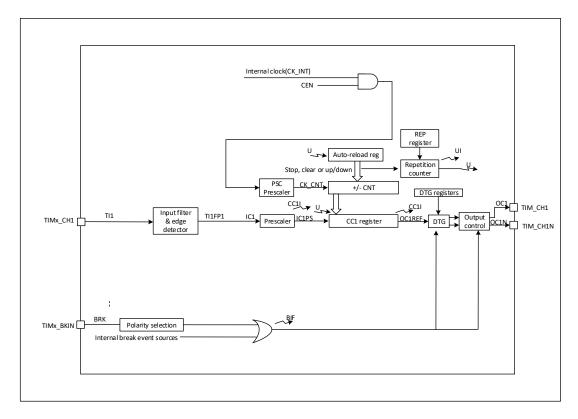

| 25. Gen | eral-purpose timers (TIM15/16/17)                    | 463 |

| 25.1.   | Introduction                                         | 463 |

| 25.2.   | TIM15 main features                                  | 463 |

| 25.3.   | TIM16_17 main features                               | 464 |

| 25.4.   | TIM15_16_17 functional description                   | 465 |

| 25.4.1  | . Time base unit                                     | 465 |

| 25.4.2  | . Counter mode                                       | 466 |

| 25.4.3  | . Repetition counter                                 | 469 |

| 25.4.4  | . Clock source                                       | 470 |

| 25.4.5  | . Capture/Compare Channel                            | 472 |

| 25.4.6  | . Input Capture mode                                 | 473 |

| 25.4.7  | . PWM input mode (TIM15 only)                        | 474 |

| 25.4.8  | . Forced output mode                                 | 475 |

| 25.4.9  | Output compare mode                                  | 476 |

| 25.4.1  | 0. PWM mode                                          | 477 |

| 25.4.  | 11. Complementary outputs and dead-time insertion              | 478 |

|--------|----------------------------------------------------------------|-----|

| 25.4.  | 12. Using the brake function                                   | 479 |

| 25.4.  | 13. One-pulse mode                                             | 481 |

| 25.5.  | TIMx timer and external trigger synchronization (TIM15 only)   | 483 |

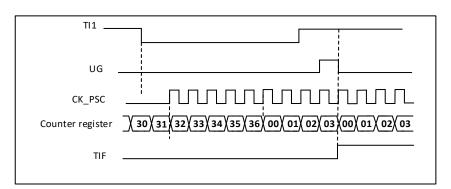

| 25.5.  | Slave mode: Reset mode                                         | 483 |

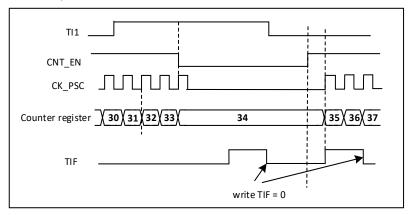

| 25.5.  | 2. Slave mode: Gated mode                                      | 484 |

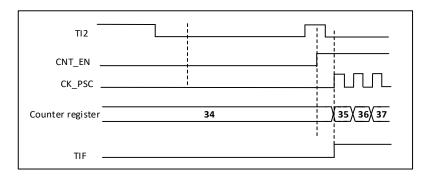

| 25.5.3 | 3. Slave mode: Trigger mode                                    | 484 |

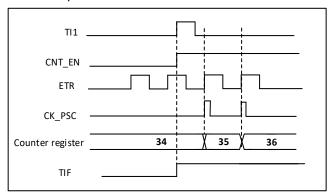

| 25.5.  | 4. Slave mode: External clock mode 2 + Trigger mode            | 485 |

| 25.5.  | 5. TIM and external trigger synchronization                    | 486 |

| 25.6.  | Timer synchronization (TIM15 only)                             | 489 |

| 25.6.  | Using one timer as a prescaler for another timer               | 489 |

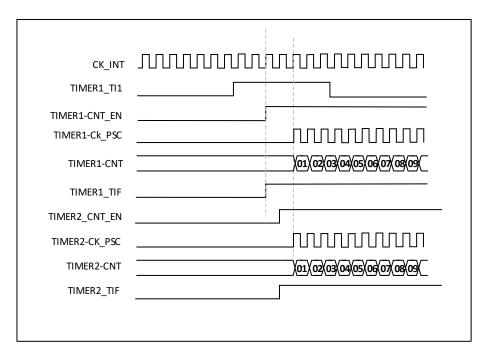

| 25.6.2 | 2. Using one timer to enable another timer                     | 490 |

| 25.6.3 | 3. Using one timer to start another timer                      | 491 |

| 25.6.  | 4. Using an external trigger to synchronously start two timers | 492 |

| 25.6.  | 5. Debug mode                                                  | 493 |

| 25.7.  | TIM15 register description                                     | 493 |

| 25.7.  | 1. TIM15 control register 1 (TIMx_CR1)                         | 493 |

| 25.7.  | 2. TIM15 control register 2 (TIMx_CR2)                         | 495 |

| 25.7.  | 3. TIM15 slave mode control register (TIMx_SMCR)               | 497 |

| 25.7.  | 4. TIM15 DMA/Interrupt Enable Register (TIMx_DIER)             | 499 |

| 25.7.  | 5. TIM15 status register (TIMx_SR)                             | 500 |

| 25.7.  | 5. TIM15 event generation register (TIMx_EGR)                  | 502 |

| 25.7.  | 7. TIM15 Capture/Compare Mode Register 1 (TIMx_CCMR1)          | 503 |

| 25.7.  | 3. TIM15 Capture/Compare Enable Register (TIMx_CCER)           | 507 |

| 25.7.  | 9. TIM15 counter (TIMx_CNT)                                    | 511 |

| 25.7.  | 10. TIM15 prescaler (TIMx_PSC)                                 | 511 |

| 25.7.  | 11. TIM15 auto-reload register (TIMx_ARR)                      | 511 |

| 25.7.  | 12. TIM15 repetition counter register (TIMx_RCR)               | 512 |

| 25.7.  | 13. TIM15 Capture/Compare Register 1 (TIMx_CCR1)               | 512 |

| 25.7.  | 14. TIM15 Capture/Compare Register 2 (TIMx_CCR2)               | 513 |

| 25.7.  | 15. TIM15 brake and dead-time register (TIMx_BDTR)             | 514 |

| 25.7.  | 16. TIM15 DMA control register (TIMx_DCR)                      | 516 |

| 25.7.  | 17. DMA address for TIM15 continuous mode (TIMx_DMAR)          | 518 |

| 25.8.  | TIM16_17 Register Description                                  | 518 |

| 25.8.  | 1. TIM16_17 Control Register 1 (TIMx_CR1)                      | 518 |

| 25.8.  | 2. TIM16_17 Control Register 2 (TIMx_CR2)                      | 520 |

| 25.8.  | 3. TIM16_17 DMA/Interrupt Enable Register (TIMx_DIER)          | 521 |

| 25.8.  | 4. TIM16_17 Status Register (TIMx_SR)                          | 522 |

| 25.8.  | 5. TIM16_17 Event Generation Register (TIMx_EGR)               | 524 |

| 25.8.0 | 6. TIM16 17 Capture/Compare Mode Register 1 (TIMx CCMR1)       | 525 |

|     | 25.8.7 | TIM16_17 Capture/Compare Enable Register (TIMx_CCER)    | 528 |

|-----|--------|---------------------------------------------------------|-----|

|     | 25.8.8 | TIM16_17 counter (TIMx_CNT)                             | 531 |

|     | 25.8.9 | TIM16_17 prescaler (TIMx_PSC)                           | 531 |

|     | 25.8.1 | D. TIM16_17 auto-reload register (TIMx_ARR)             | 532 |

|     | 25.8.1 | 1. TIM16_17 repetition counter register (TIMx_RCR)      | 532 |

|     | 25.8.1 | 2. TIM16_17 Capture/Compare Register 1 (TIMx_CCR1)      | 533 |

|     | 25.8.1 | 3. TIM16_17 Brake and Dead-Time Register (TIMx_BDTR)    | 533 |

|     | 25.8.1 | 4. TIM16_17 DMA control register (TIMx_DCR)             | 536 |

|     | 25.8.1 | 5. DMA address for TIM16_17 continuous mode (TIMx_DMAR) | 538 |

| 26. | Low    | -power Timer (LPTIM)                                    | 539 |

| 2   | 6.1.   | Introduction                                            | 539 |

| 2   | 6.2.   | LPTIM Key Features                                      | 539 |

| 2   | 6.3.   | Low-power Timer (LPTIM) Functional Description          | 539 |

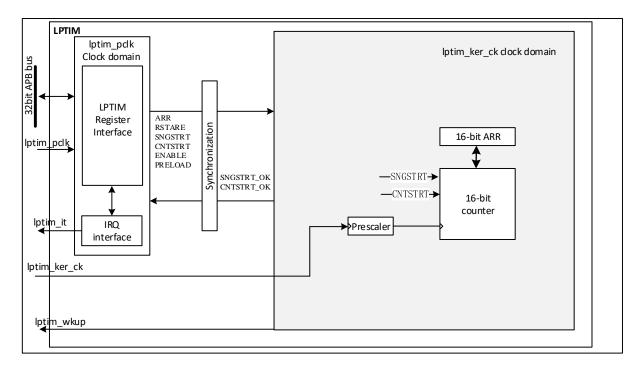

|     | 26.3.1 | LPTIM Block Diagram                                     | 539 |

|     | 26.3.2 | LPTIM Pins and Internal Signals                         | 539 |

|     | 26.3.3 | LPTIM Reset and Clock                                   | 540 |

|     | 26.3.4 | Prescaler                                               | 540 |

|     | 26.3.5 | Operating mode                                          | 540 |

|     | 26.3.6 | Register update                                         | 541 |

|     | 26.3.7 | Counter mode                                            | 541 |

|     | 26.3.8 | Counter reset                                           | 541 |

|     | 26.3.9 | Debug mode                                              | 542 |

| 2   | 6.4.   | LPTIM low-power modes                                   | 542 |

| 2   | 6.5.   | LPTIM interrupt                                         | 542 |

| 2   | 6.6.   | LPTIM registers                                         | 542 |

|     | 26.6.1 | LPTIM interrupt and status register (LPTIM_ISR)         | 542 |

|     | 26.6.2 | LPTIM Interrupt Clear Register (LPTIM_ICR)              | 543 |

|     | 26.6.3 | LPTIM Interrupt Enable Register (LPTIM_IER)             | 544 |

|     | 26.6.4 | LPTIM configuration register (LPTIM_CFGR)               | 544 |

|     | 26.6.5 | LPTIM control register (LPTIM_CR)                       | 545 |

|     | 26.6.6 | LPTIM auto-reload register (LPTIM_ARR)                  | 546 |

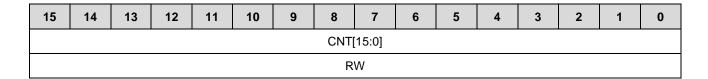

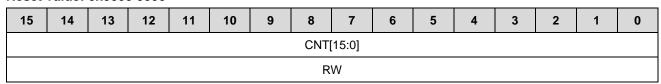

|     | 26.6.7 | LPTIM counter register (LPTIM_CNT)                      | 547 |

| 27. | Inde   | pendent watchdog (IWDG)                                 | 548 |

| 2   | 7.1.   | Introduction                                            | 548 |

| 2   | 7.2.   | IWDG key features                                       | 548 |

| 2   | 7.3.   | IWDG functional description                             | 548 |

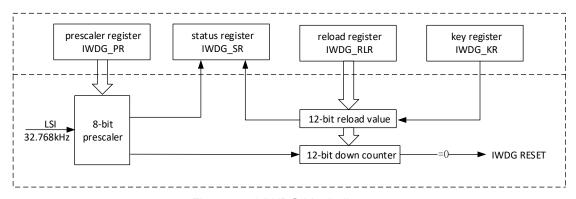

|     | 27.3.1 | IWDG block diagram                                      | 548 |

|     | 27.3.2 | Hardware watchdog                                       | 549 |

|     | 27.3.3 | Register protection                                     | 549 |

|     | 27 3 4 | Debug mode and STOP mode                                | 549 |

| 2   | 7.4.     | IWDG registers                                        | 550 |

|-----|----------|-------------------------------------------------------|-----|

|     | 27.4.1.  | Key Register (IWDG_KR)                                | 550 |

|     | 27.4.2.  | Prescaler register (IWDG_PR)                          | 550 |

|     | 27.4.3.  | Reload register (IWDG_RLR)                            | 551 |

|     | 27.4.4.  | Status register (IWDG_SR)                             | 552 |

| 28. | Win      | dow Watchdog (WWDG)                                   | 553 |

| 2   | 8.1.     | Introduction                                          | 553 |

| 2   | 8.2.     | WWDG Key Features                                     | 553 |

| 2   | 8.3.     | WWDG Functional Description                           | 553 |

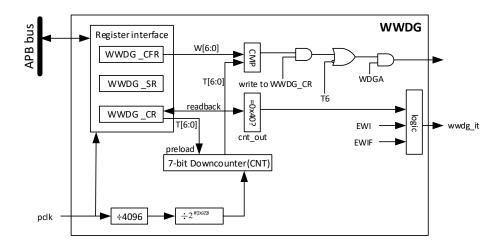

|     | 28.3.1.  | WWDG block diagram                                    | 554 |

|     | 28.3.2.  | Activate the watchdog                                 | 554 |

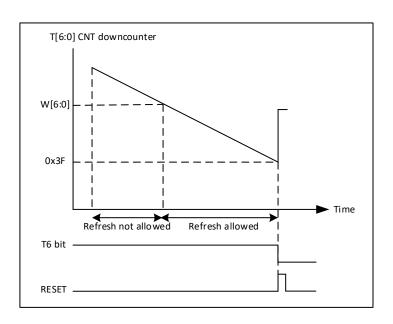

|     | 28.3.3.  | Control the downcounter                               | 554 |

|     | 28.3.4.  | Advanced watchdog interrupt function                  | 555 |

|     | 28.3.5.  | How to program the watchdog timeout                   | 555 |

|     | 28.3.6.  | Debug mode                                            | 556 |

| 2   | 8.4.     | WWDG registers                                        | 556 |

|     | 28.4.1.  | Control register (WWDG_CR)                            | 556 |

|     | 28.4.2.  | Configuration register (WWDG_CFR)                     | 556 |

|     | 28.4.3.  | Status Register (WWDG_SR)                             | 557 |

| 29. | Rea      | l-Time Clock (RTC)                                    | 558 |

| 2   | 9.1.     | Introduction                                          | 558 |

| 2   | 9.2.     | RTC main features                                     | 558 |

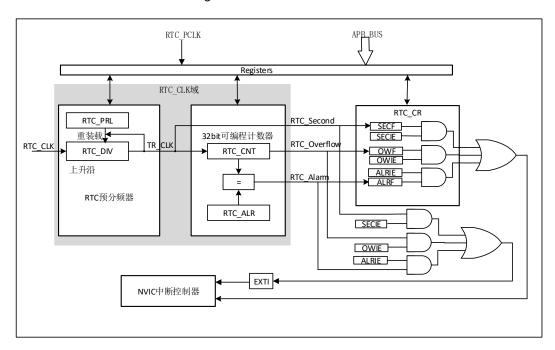

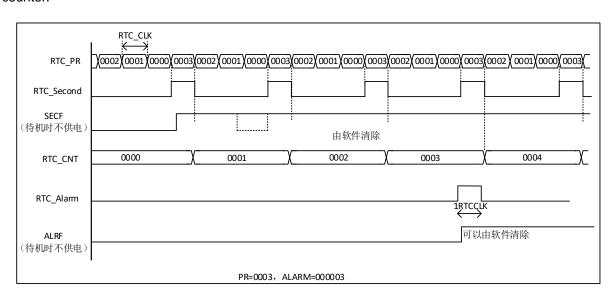

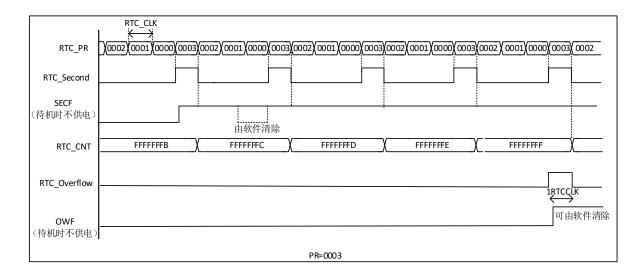

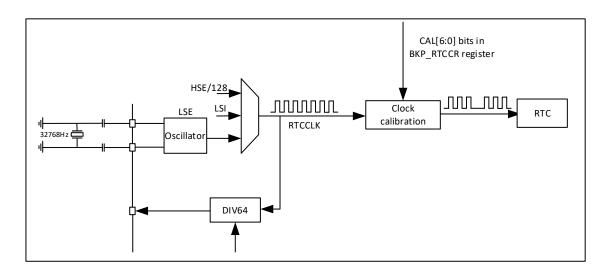

| 2   | 9.3.     | RTC functional description                            | 558 |

|     | 29.3.1.  | Overview                                              | 558 |

|     | 29.3.2.  | Reset RTC registers                                   | 559 |

|     | 29.3.3.  | Read RTC registers                                    | 559 |

|     | 29.3.4.  | Configuring RTC registers                             | 560 |

|     | 29.3.5.  | Setting of RTC Flags                                  | 561 |

|     | 29.3.6.  | RTC Calibration                                       | 562 |

| 2   | 9.4.     | RTC Register                                          | 562 |

|     | 29.4.1.  | RTC Control Register (RTC_CRH)                        | 562 |

|     | 29.4.2.  | RTC Control Register (RTC_CRL)                        | 563 |

|     | 29.4.3.  | RTC Prescaler Load Register (RTC_PRLH)                | 565 |

|     | 29.4.4.  | RTC Prescaler Divider Register (RTC_PRLL)             | 566 |

|     | 29.4.5.  | RTC Prescaler Divider Factor Register High (RTC_DIVH) | 567 |

|     | 29.4.6.  | RTC prescaler divider factor register low (RTC_DIVL)  | 567 |

|     | 29.4.7.  | RTC Counter Register High (RTC_CNTH)                  | 567 |

|     | 29.4.8.  | RTC counter register low bits (RTC_CNTL)              | 568 |

|     | 20. 1.0. |                                                       |     |

|     | 29.4.9.  | · · · · · · · · · · · · · · · · · · ·                 |     |

| 29.4.1   | 1. RTC clock calibration and output configuration register (BKP_RTCCR) | 570 |

|----------|------------------------------------------------------------------------|-----|

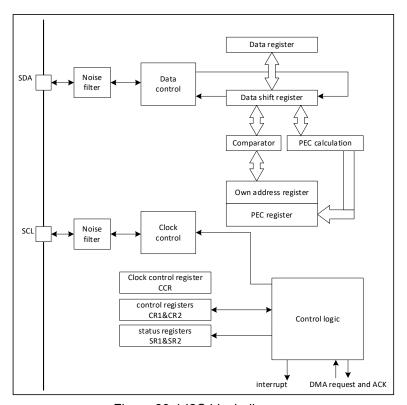

| 30. I2C  | interface                                                              | 571 |

| 30.1.    | Introduction                                                           | 571 |

| 30.2.    | I2C key features                                                       | 571 |

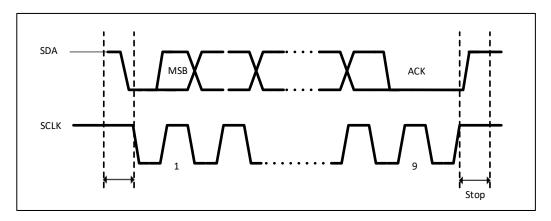

| 30.3.    | I2C functional description                                             | 572 |

| 30.3.1.  | I2C block diagram                                                      | 572 |

| 30.3.2.  | Mode selection                                                         | 572 |

| 30.3.3.  | I2C initialization                                                     | 573 |

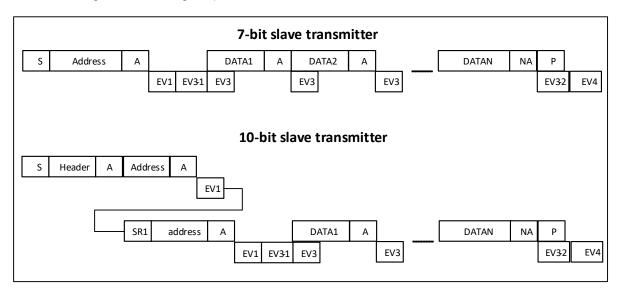

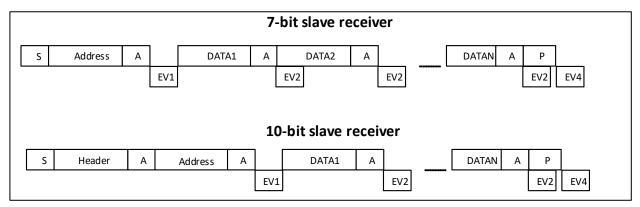

| 30.3.4.  | I2C slave mode                                                         | 573 |

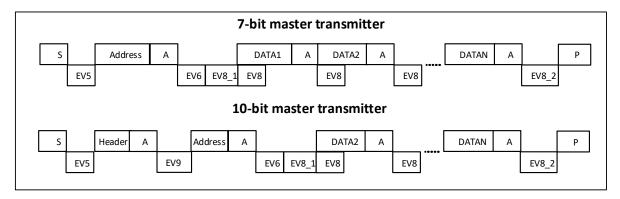

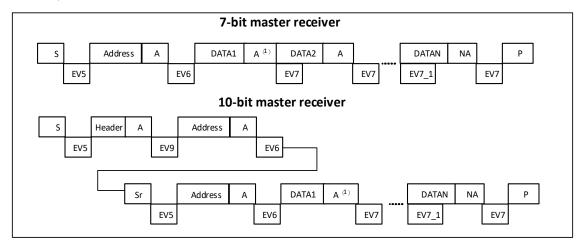

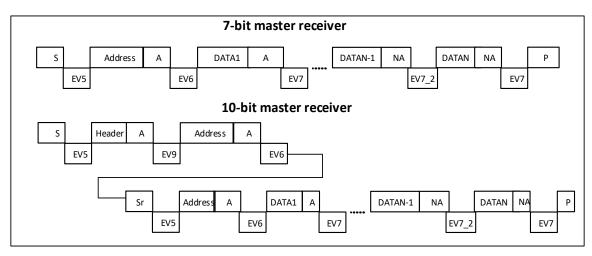

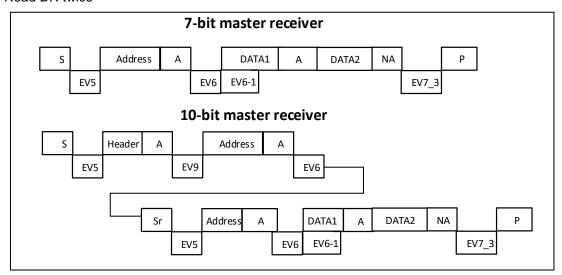

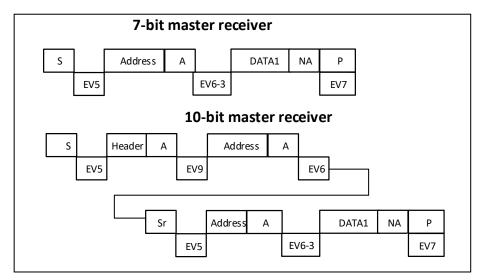

| 30.3.5.  | I2C master mode                                                        | 576 |

| 30.3.6.  | Error Status                                                           | 582 |

| 30.3.7.  | SDA/SCL Control                                                        | 583 |

| 30.3.8.  | DMA Request                                                            | 583 |

| 30.3.9.  | SMBus                                                                  | 585 |

| 30.4.    | I2C Interrupt                                                          | 587 |

| 30.5.    | I2C registers                                                          |     |

| 30.5.1.  | I2C Control Register 1 (I2C_CR1)                                       | 587 |

| 30.5.2.  | I2C Control Register 2 (I2C_CR2)                                       | 590 |

| 30.5.3.  | I2C own address register 1 (I2C_OAR1)                                  | 592 |

| 30.5.4.  | I2C Own Address Register 2 (I2C_OAR2)                                  | 593 |

| 30.5.5.  | I2C Data Register (I2C_DR)                                             | 593 |

| 30.5.6.  | I2C Status Register (I2C_SR1)                                          | 594 |

| 30.5.7.  | I2C Status Register 2 (I2C_SR2)                                        | 598 |

| 30.5.8.  | I2C Clock Control Register (I2C_CCR)                                   | 600 |

| 30.5.9.  | I2C TRISE Register (I2C_TRISE)                                         | 601 |

| 31. Seri | al Peripheral Interface (SPI)                                          | 603 |

| 31.1.    | Introduction                                                           | 603 |

| 31.2.    | SPI main features                                                      | 603 |

| 31.2.1.  | SPI main features                                                      | 603 |

| 31.2.2.  | I2S main features                                                      | 604 |

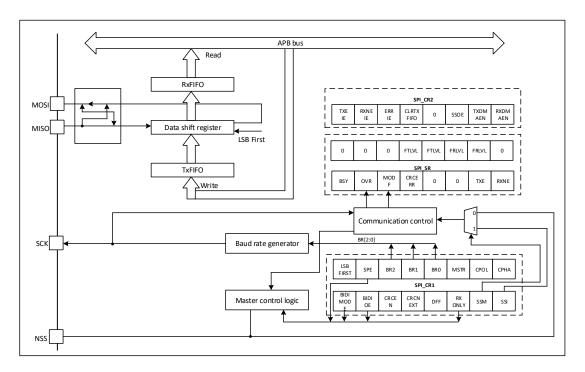

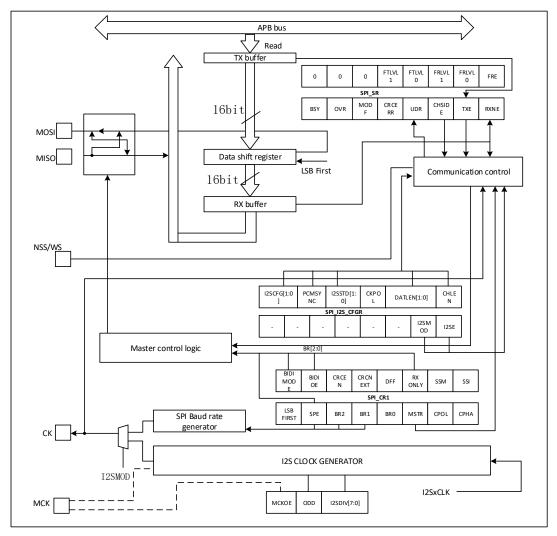

| 31.3.    | SPI functional description                                             | 605 |

| 31.3.1.  | Overview                                                               | 605 |

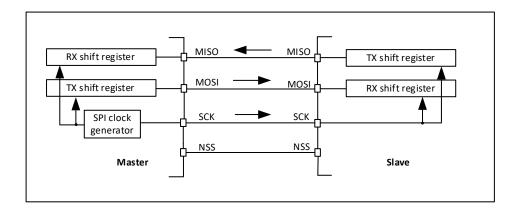

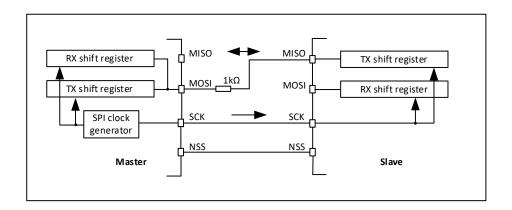

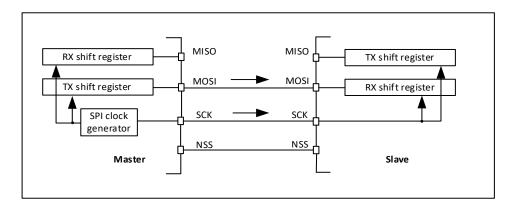

| 31.3.2.  | Single master and single slave communication                           | 605 |

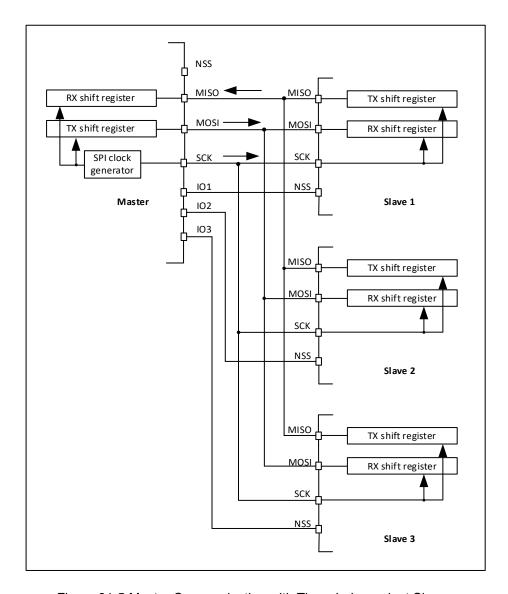

| 31.3.3.  | Multi-Slave Communication                                              | 608 |

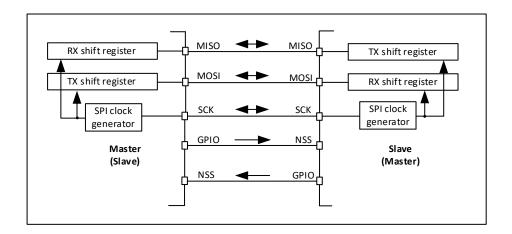

| 31.3.4.  | Multi-Master Communication                                             | 608 |

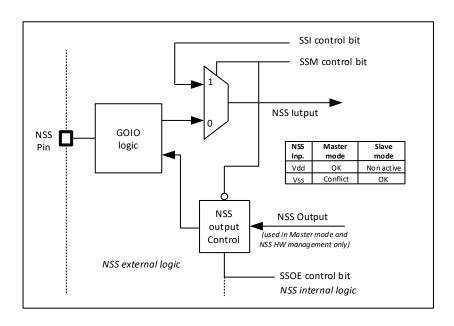

| 31.3.5.  | Slave select (NSS) pin management                                      | 609 |

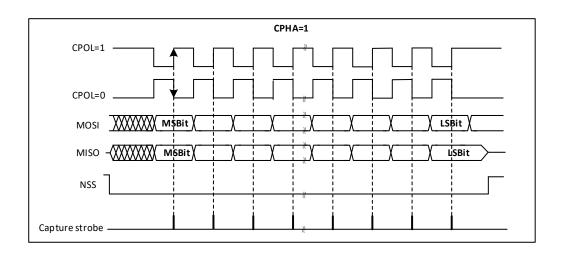

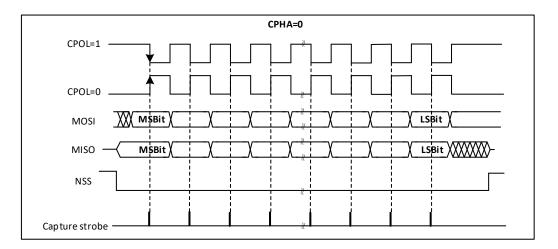

| 31.3.6.  | Communication format                                                   | 610 |

| 31.3.7.  | SPI Configuration                                                      | 611 |

| 31.3.8.  | ·                                                                      |     |

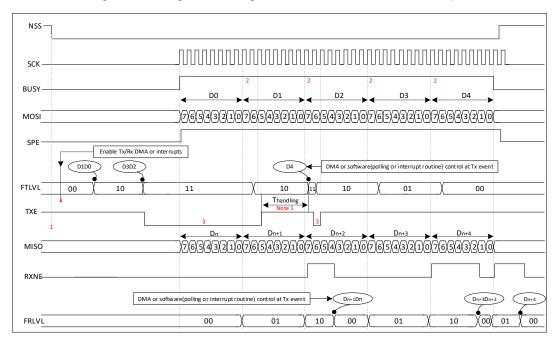

| 31.3.9.  | Data transmission and reception process                                | 612 |

|     | 31.3.10 | ). Status flags                                              | 616 |

|-----|---------|--------------------------------------------------------------|-----|

|     | 31.3.1  | l. Error Flags                                               | 617 |

|     | 31.3.12 | 2. SPI interrupt                                             | 618 |

|     | 31.3.13 | 3. CRC calculation                                           | 618 |

| 3   | 1.4.    | I2S Functional Description                                   | 620 |

|     | 31.4.1. | Overview                                                     | 620 |

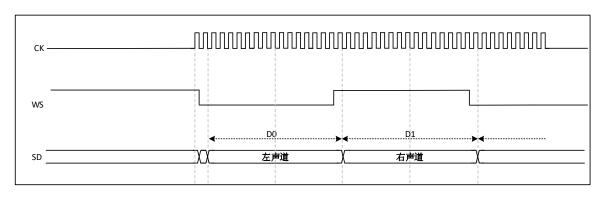

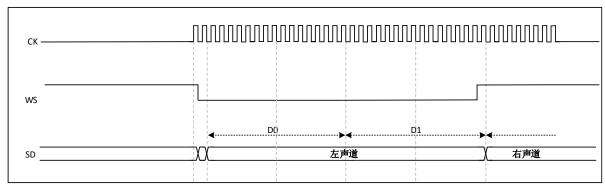

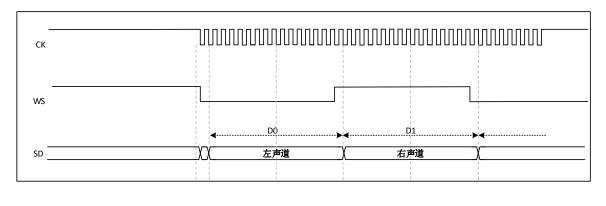

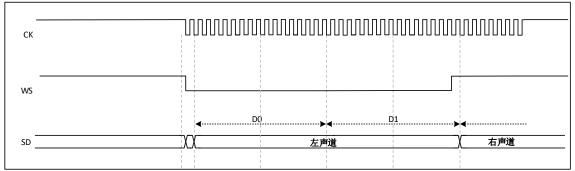

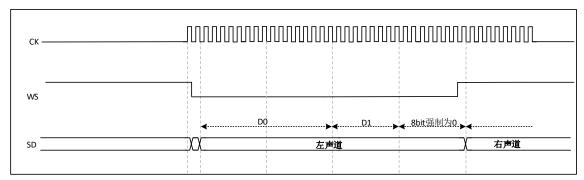

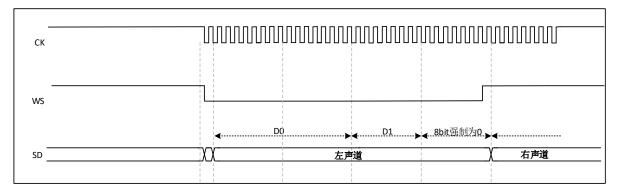

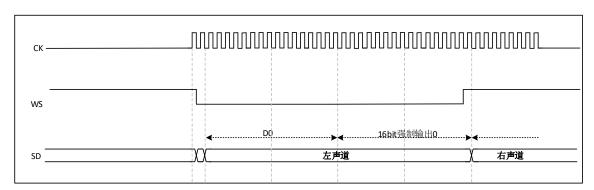

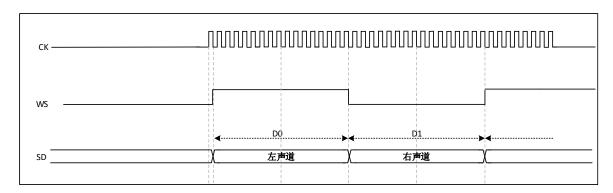

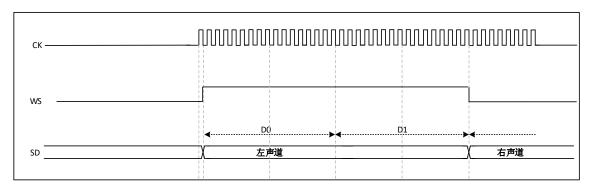

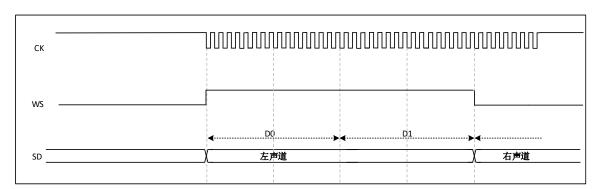

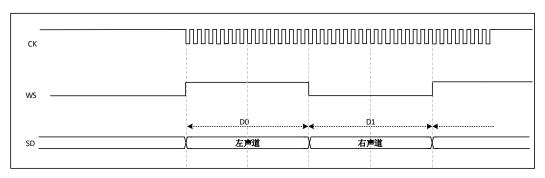

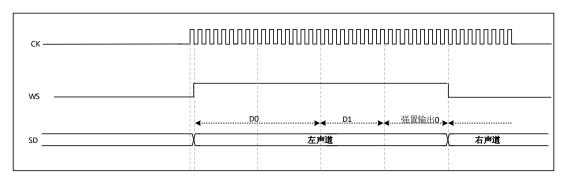

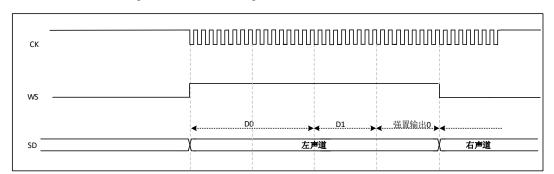

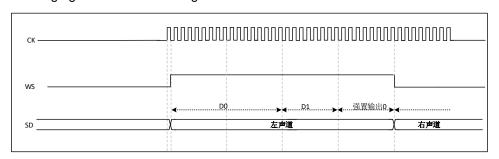

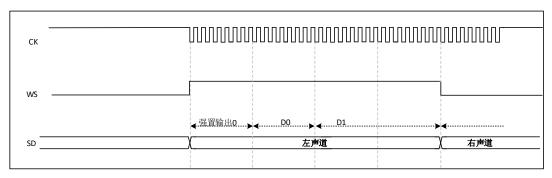

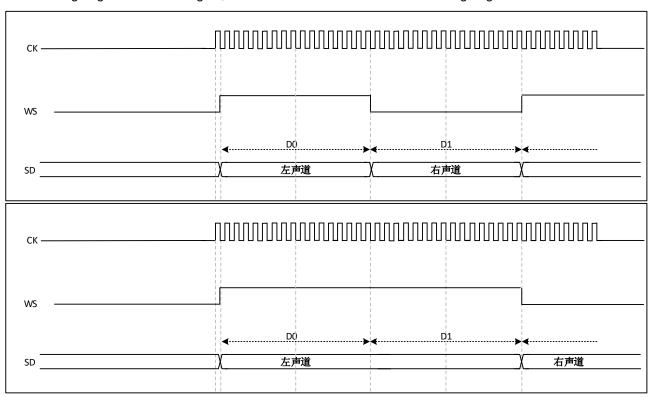

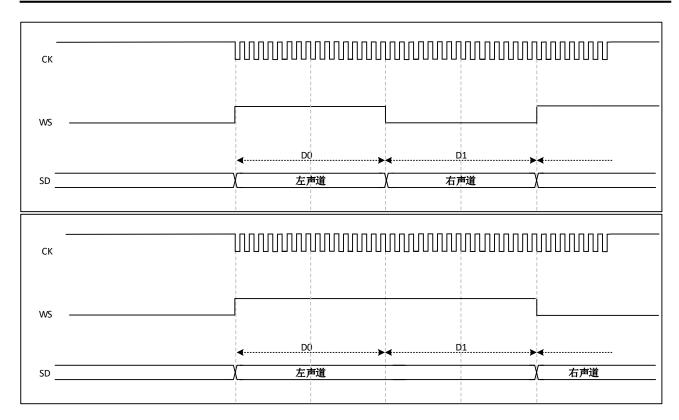

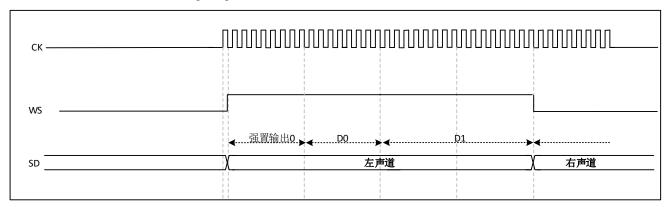

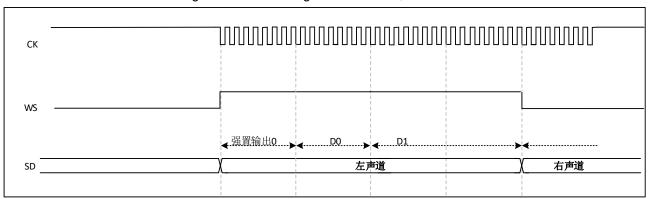

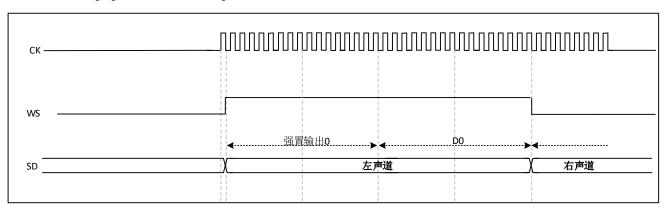

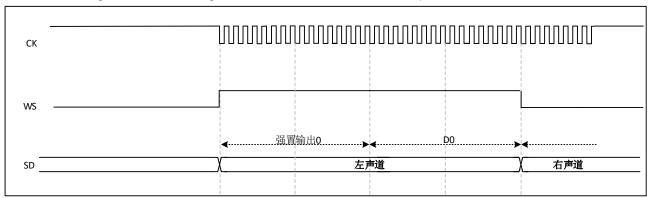

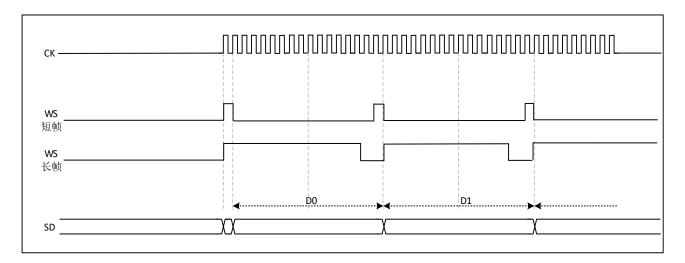

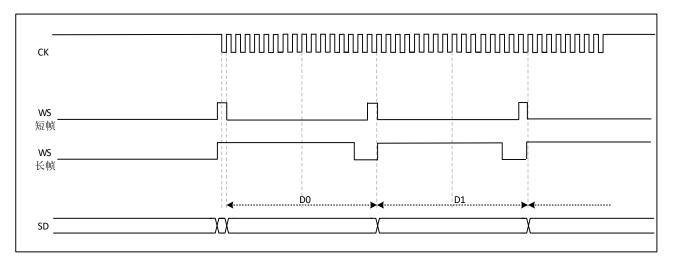

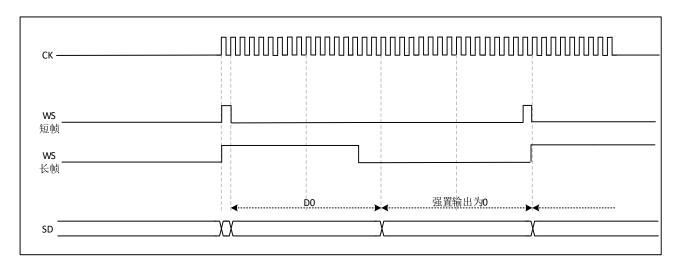

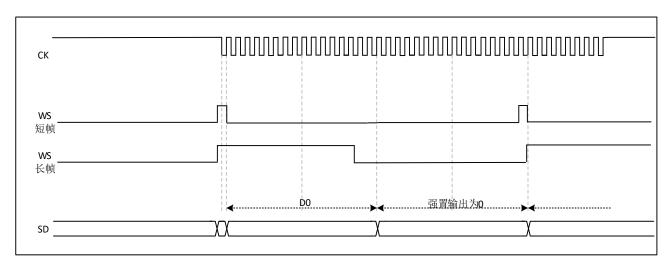

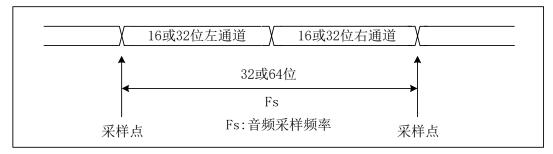

|     | 31.4.2. | Audio Protocol                                               | 621 |

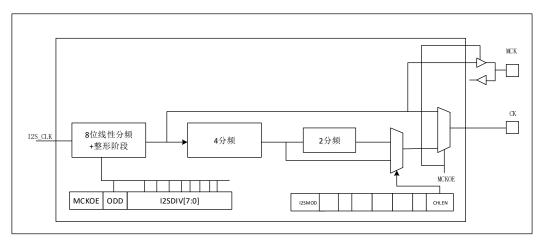

|     | 31.4.3. | Clock Generator                                              | 630 |

|     | 31.4.4. | I2S Master Mode                                              | 632 |

|     | 31.4.5. | I2S Slave Mode                                               | 634 |

|     | 31.4.6. | Error flags                                                  | 636 |

|     | 31.4.7. | I2S interrupt                                                | 636 |

|     | 31.4.8. | DMA Function                                                 | 636 |

| 3   | 1.5.    | SPI and I2S Registers                                        | 636 |

|     | 31.5.1. | SPI Control Register 1 (SPI_CR1) (Not used in I2S mode)      | 637 |

|     | 31.5.2. | SPI Control Register 2 (SPI_CR2)                             | 639 |

|     | 31.5.3. | SPI Status Register (SPI_SR)                                 | 641 |

|     | 31.5.4. | SPI Data Register (SPI_DR)                                   | 642 |

|     | 31.5.5. | SPI CRC polynomial register (SPI_CRCPR)                      | 643 |

|     | 31.5.6. | SPI Rx CRC Register (SPI_RXCRCR)                             | 643 |

|     | 31.5.7. | SPI Tx CRC Register (SPI_TXCRCR)                             | 644 |

|     | 31.5.8. | SPI_I2S Configuration Register (SPI_I2S_CFGR)                | 645 |

|     | 31.5.9. | SPI_I2S Prescaler Register (SPI_I2SPR)                       | 646 |

| 32. | Univ    | rersal Synchronous Asynchronous Receiver Transmitter (USART) | 648 |

| 3   | 2.1.    | Introduction                                                 | 648 |

| 3   | 2.2.    | USART main features                                          | 648 |

| 3   | 2.3.    | USART functional description                                 | 649 |

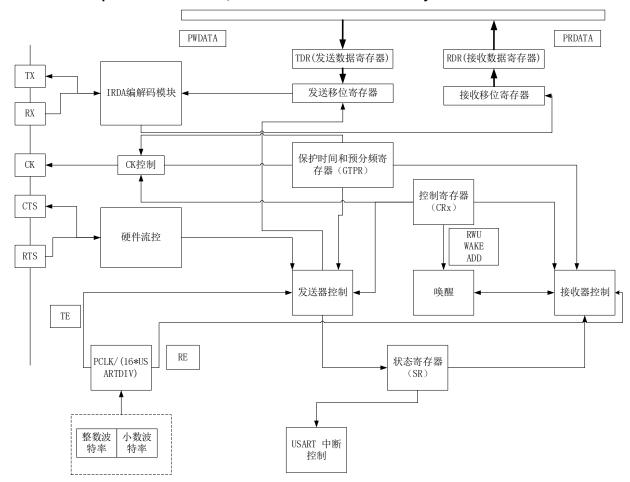

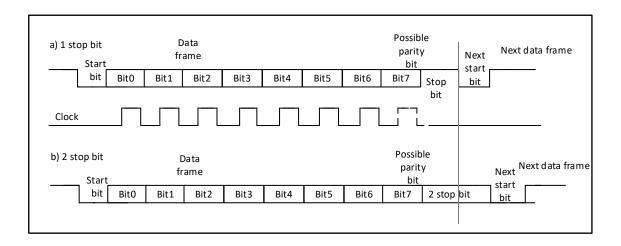

|     | 32.3.1. | USART feature description                                    | 650 |

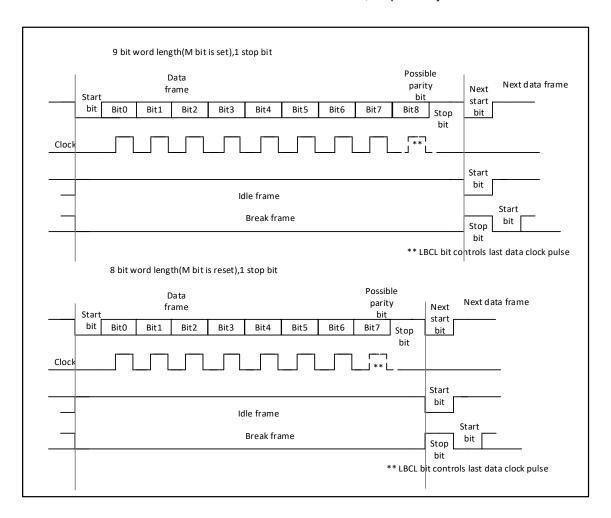

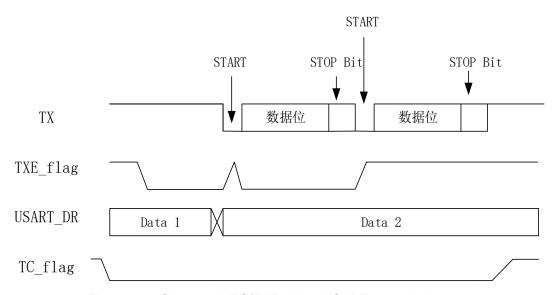

|     | 32.3.2. | Transmitter                                                  | 651 |

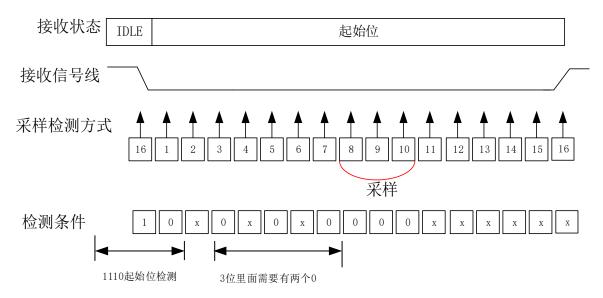

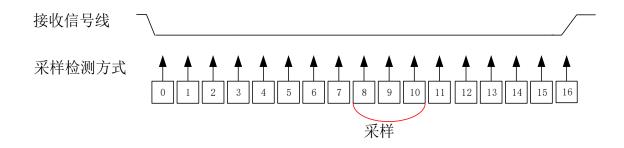

|     | 32.3.3. | Receiver                                                     | 654 |

|     | 32.3.4. | Fractional baud rate generation                              | 657 |

|     | 32.3.5. | USART receiver tolerance                                     | 658 |

|     | 32.3.6. | USART auto-baud rate detection                               | 659 |

|     | 32.3.7. | Multiprocessor communication                                 | 660 |

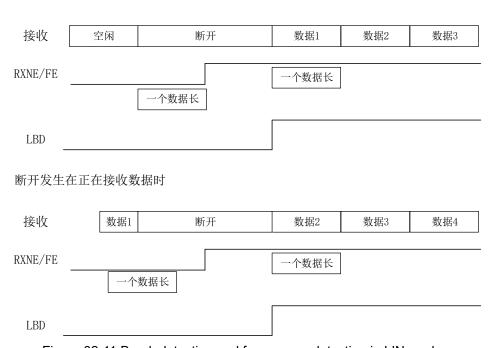

|     | 32.3.8. | LIN (Local Interconnect Network) mode                        | 662 |

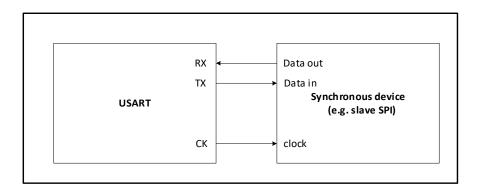

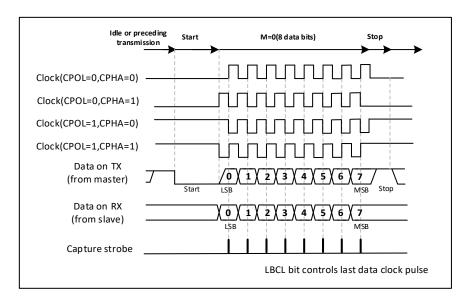

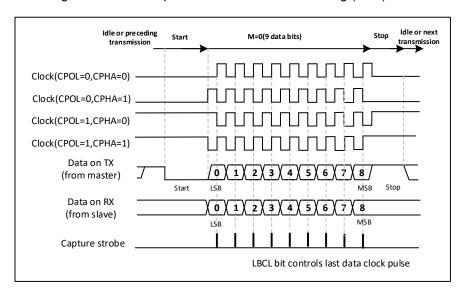

|     | 32.3.9. | USART Synchronous Mode                                       | 663 |

|     | 32.3.10 | ). Single-wire half-duplex communication                     | 665 |

|     | 32.3.1  | Smart Card                                                   | 666 |

|     | 32.3.12 | 2. IrDA SIR ENDEC Functional Block                           | 667 |

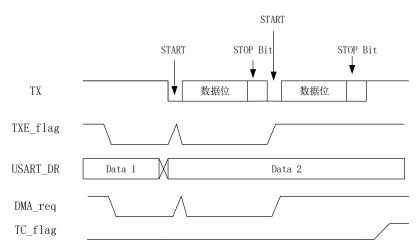

|     | 32.3.13 | B. Continuous communication using DMA                        | 669 |

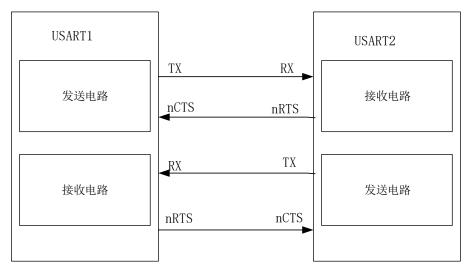

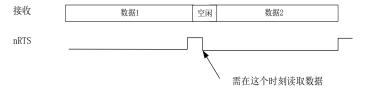

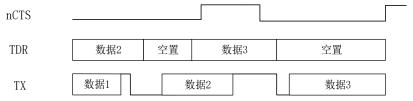

| 32   | 2.3.14. | Hardware flow control                                       | 671 |

|------|---------|-------------------------------------------------------------|-----|

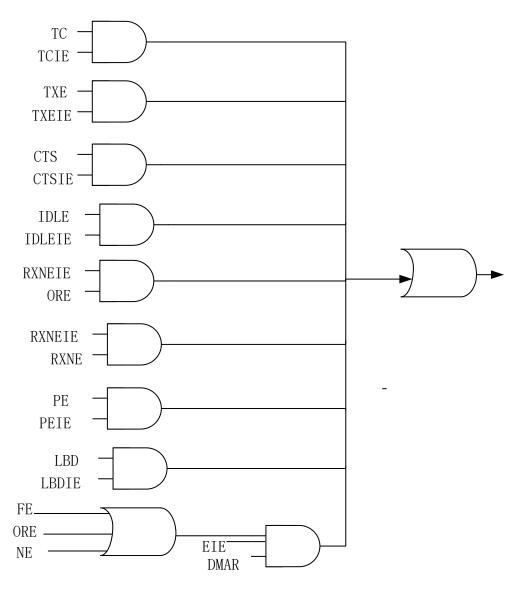

| 32.4 | ι. ι    | JSART interrupt request                                     | 672 |

| 32.5 | ί. ι    | JSART Registers                                             | 673 |

| 32   | 2.5.1.  | Status Register (USART_SR)                                  | 673 |

| 32   | 2.5.2.  | Data Register (USART_DR)                                    | 677 |

| 32   | 2.5.3.  | Baud rate register (USART_BRR)                              | 678 |

| 32   | 2.5.4.  | Control register 1 (USART_CR1)                              | 678 |

| 32   | 2.5.5.  | Control register 2 (USART_CR2)                              | 680 |

| 32   | 2.5.6.  | Control Register 3 (USART_CR3)                              | 682 |

| 32   | 2.5.7.  | Guard time and prescaler (USART_GTPR)                       | 684 |

| 33.  | CAN2    | 2.0 controller                                              | 686 |

| 33.1 | . 1     | ntroduction                                                 | 686 |

| 33.2 | c       | CAN main features                                           | 686 |

| 33.3 | s. C    | CAN functional description                                  | 687 |

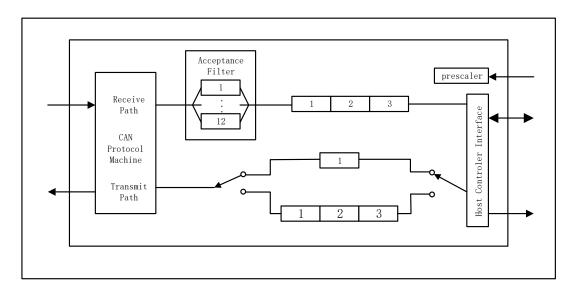

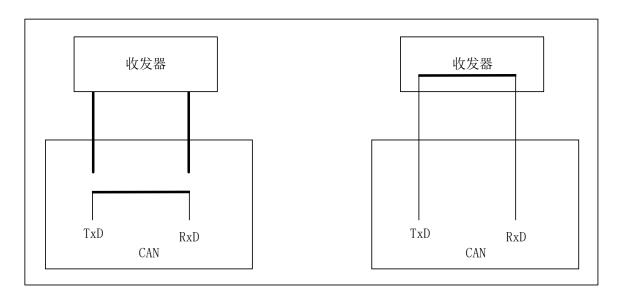

| 33   | 3.3.1.  | Block diagram                                               | 687 |

| 33   | 3.3.2.  | Active mode                                                 | 687 |

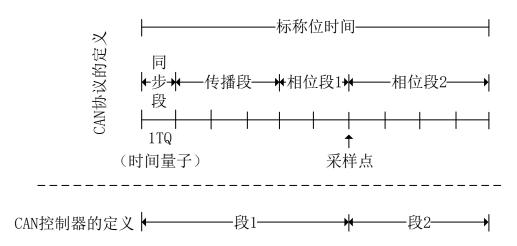

| 33   | 3.3.3.  | Baud rate configuration                                     | 687 |

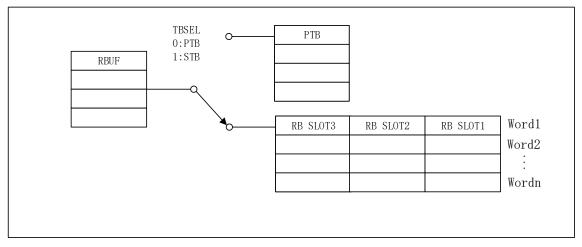

| 33   | 3.3.4.  | Transmit Buffer                                             | 689 |

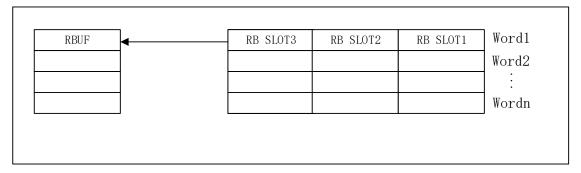

| 33   | 3.3.5.  | Receive Buffer                                              | 690 |

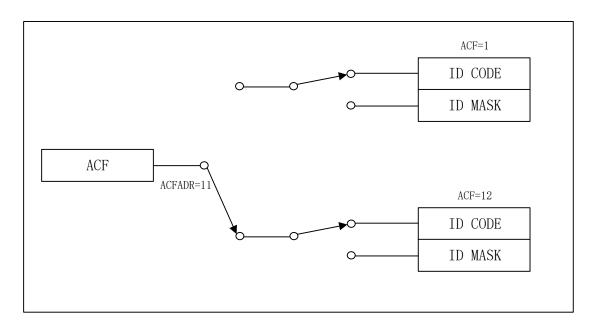

| 33   | 3.3.6.  | Receive Filter Register Group                               | 690 |

| 33   | 3.3.7.  | LLC Frame Format Definition                                 | 691 |

| 33   | 3.3.8.  | Data transmission                                           | 693 |

| 33   | 3.3.9.  | Cancel Data Transmission                                    | 693 |

| 33   | 3.3.10. | Data Reception                                              | 694 |

| 33   | 3.3.11. | Error Handling                                              | 694 |

| 33   | 3.3.12. | Bus-off                                                     | 695 |

| 33   | 3.3.13. | Arbitration failure position capture                        | 695 |

| 33   | 3.3.14. | Loopback mode                                               | 695 |

| 33   | 3.3.15. | Silent mode                                                 | 696 |

| 33   | 3.3.16. | Software Reset Function                                     | 696 |

| 33   | 3.3.17. | Time-Triggered TTCAN                                        | 698 |

| 33   | 3.3.18. | Interrupt                                                   | 700 |

| 33.4 | . F     | Register description                                        | 701 |

| 33   | 3.4.1.  | Node configuration register (CAN_TSNCR)                     | 701 |

| 33   | 3.4.2.  | Bit timing configuration register (CAN_ACBTR)               | 702 |

| 33   | 3.4.3.  | Limitation and Prescaler Configuration Register (CAN_RLSSP) | 702 |

| 33   | 3.4.4.  | Status Register (CAN_IFR)                                   | 703 |

| 33   | 3.4.5.  | Interrupt Enable Register (CAN_IER)                         | 706 |

| 33   | 3.4.6.  | Transmission Status Register (CAN_TSR)                      | 707 |

| 33   | 3.4.7.  | Global Configuration Register (CAN MCR)                     | 707 |

|     | 33.4.8. | Error Warning Register (CAN_WECR)                 | 713 |

|-----|---------|---------------------------------------------------|-----|

|     | 33.4.9. | Reference ID Register (CAN_REFMSG)                | 714 |

|     | 33.4.10 | ). TTCAN Configuration Register (CAN_TTCR)        | 715 |

|     | 33.4.1  | I. TTCAN Trigger Register (CAN_TTTR)              | 717 |

|     | 33.4.12 | 2. Memory Status Register (CAN_SCMS)              | 717 |

|     | 33.4.13 | Filter group control register (CAN_ACFCR)         | 719 |

|     | 33.4.14 | Filter group code register (CAN_ACFC)             | 719 |

|     | 33.4.1  | 5. Filter Group Mask Register (CAN_ACFM)          | 720 |

|     | 33.4.16 | 6. CAN Receive Buffer Register (CAN_RBUF)         | 720 |

|     | 33.4.17 | 7. CAN Transmit Buffer Register (CAN_TBUF)        | 720 |

| 34. | USE     | Full-Speed Device Interface (USBD)                | 721 |

| 3   | 4.1.    | Introduction                                      | 721 |

| 3   | 4.2.    | Key Features of USB                               | 721 |

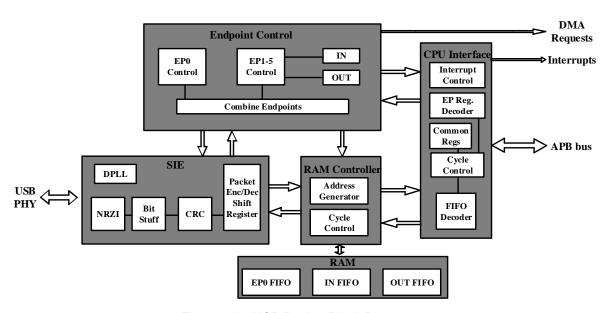

| 3   | 4.3.    | USB Device Block Diagram                          | 721 |

| 3   | 4.4.    | Functional Description                            | 721 |

|     | 34.4.1. | Functional Module Description                     | 722 |

|     | 34.4.2. | System reset and power-on reset                   | 722 |

|     | 34.4.3. | USB reset state                                   | 722 |

|     | 34.4.4. | USB suspend/wakeup mode                           | 723 |

|     | 34.4.5. | IN packet (for data transmission)                 | 723 |

|     | 34.4.6. | OUT packets (used for data reception)             | 724 |

|     | 34.4.7. | Control Transfer                                  | 724 |

|     | 34.4.8. | Isochronous transfer                              | 727 |

|     | 34.4.9. | Bulk transfer                                     | 731 |

|     | 34.4.10 | ). Interrupt transfer                             | 734 |

| 3   | 4.5.    | USB registers                                     | 735 |

|     | 34.5.1. | USB Control Register (USB_CR)                     | 735 |

|     | 34.5.2. | USB Interrupt Status Register (USB_INTR)          | 736 |

|     | 34.5.3. | USB Interrupt Enable Register (USB_INTRE)         | 737 |

|     | 34.5.4. | USB Frame Register (USB_FRAME)                    | 738 |

|     | 34.5.5. | USB Endpoint 0 Control Register (USB_EP0CSR)      | 738 |

|     | 34.5.6. | USB IN Endpoint Control Register (USB_INEPxCSR)   | 739 |

|     | 34.5.7. | USB OUT endpoint control register (USB_OUTEPxCSR) | 741 |

|     | 34.5.8. | USB OUT Endpoint Count Register (USB_OUTCOUNT)    | 742 |

|     | 34.5.9. | 5 · · · - · ·                                     |     |

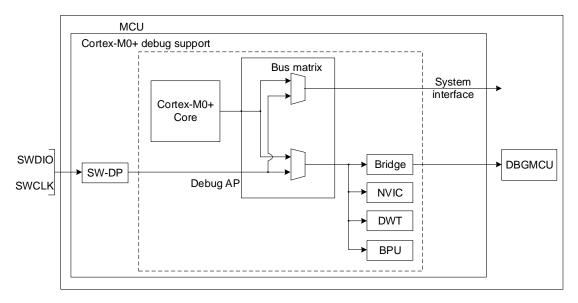

| 35. | Deb     | ug Support                                        | 744 |

| 3   | 5.1.    | Overview                                          |     |

| 3   | 5.2.    | Pin distribution and debug port pins              | 744 |

|     | 35.2.1. | <del>o</del>                                      |     |

|     | 35.2.2  | Flexible SW-DP pin assignment                     | 745 |

|     | 35.2.3. | Internal pull-up and pull-down on SWD pins              | 745 |

|-----|---------|---------------------------------------------------------|-----|

| 3   | 5.3. I  | D code and locking mechanism                            | 745 |

| 3   | 5.4.    | SWD Debug Port                                          | 745 |

|     | 35.4.1. | SWD Protocol Introduction                               | 745 |

|     | 35.4.2. | SWD Protocol Sequence                                   | 745 |

|     | 35.4.3. | SW-DP state machine (reset, idle states, ID code)       | 746 |

|     | 35.4.4. | DP and AP read/write accesses                           | 746 |

|     | 35.4.5. | SW-DP registers                                         | 747 |

|     | 35.4.6. | SW-AP register                                          | 747 |

| 3   | 5.5. (  | Core Debug                                              | 748 |

| 3   | 5.6. I  | 3PU Breakpoint Unit (Break Point Unit)                  | 748 |

|     | 35.6.1. | BPU Functionality                                       | 748 |

| 3   | 5.7. I  | Data Watchpoint DWT (Data Watchpoint)                   | 748 |

|     | 35.7.1. | DWT Functionality                                       | 748 |

|     | 35.7.2. | DWT Program Counter Sample Register                     | 749 |

| 3   | 5.8. I  | MCU Debug Module (DBGMCU)                               | 749 |

|     | 35.8.1. | Debug Support for Low-Power Modes                       | 749 |

|     | 35.8.2. | Supports debugging for timers, watchdogs, CAN, and I2C. | 749 |

| 3   | 5.9. I  | DBG Register                                            | 750 |

|     | 35.9.1. | DBG Device ID Code Register (DBG_IDCODE)                | 750 |

|     | 35.9.2. | Debug MCU Configuration Register (DBGMCU_CR)            | 750 |

|     | 35.9.3. | DBG APB Freeze Register 1 (DBG_APB_FZ1)                 | 751 |

|     | 35.9.4. | DBG APB Freeze Register 2 (DBG_APB_FZ2)                 | 753 |

| 36. | Versi   | on History                                              | 755 |

# 1. List of abbreviations for register

| Abbreviation                                                                                                        | Descriptions                                                                                       |

|---------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

| Read/write (rw)                                                                                                     | Software can read and write to this bit.                                                           |

| Read-only (r)                                                                                                       | Software can only read this bit.                                                                   |

| Write-only (w)                                                                                                      | Software can only write to this bit. Reading this bit returns the reset value.                     |

| Read/clear write0 (rc_w0)                                                                                           | Software can read as well as clear this bit by writing 0. Writing '1' has no effect on the bit     |

| inead/clear writeo (10_wo)                                                                                          | value.                                                                                             |

| Read/clear write1 (rc_w1)                                                                                           | Software can read as well as clear this bit by writing 1. Writing '0' has no effect on the bit     |

| Read/clear write (10_w1)                                                                                            | value.                                                                                             |

| Read/clear write (rc_w) Software can read as well as clear this bit by writing register. Writing to this bit has no |                                                                                                    |

| Read/clear by read (rc_r)                                                                                           | Software can read this bit. Reading this bit automatically clears it to '0'. Writing this bit has  |

| inead/clear by read (ic_i)                                                                                          | no effect on the bit value.                                                                        |

| Read/set by read (rs_r)                                                                                             | The software can read this bit. Reading this bit automatically sets it to 1. Writing this bit does |

| inead/set by read (is_i)                                                                                            | not affect the bit value.                                                                          |

| Read/set (rs)                                                                                                       | Software can read as well as set this bit to '1'. Writing '0' has no effect on the bit value.      |

| Toggle (t)                                                                                                          | Software can toggle this bit by writing '1'. Writing '0' has no effect.                            |

| Reserved (Res)                                                                                                      | Reserved bit, must be kept at reset value.                                                         |

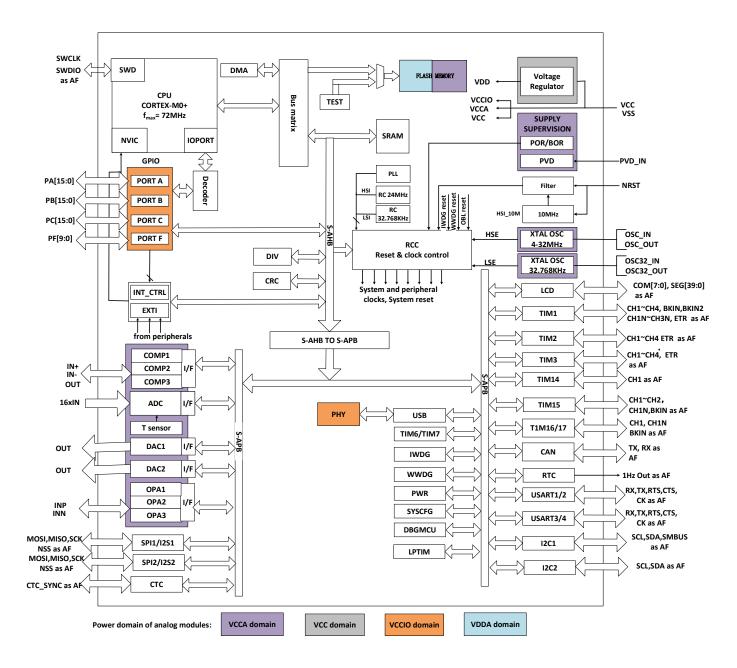

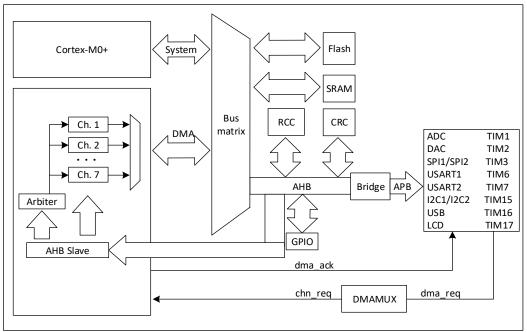

# 2. System architecture

Figure 2-1 System architecture diagram

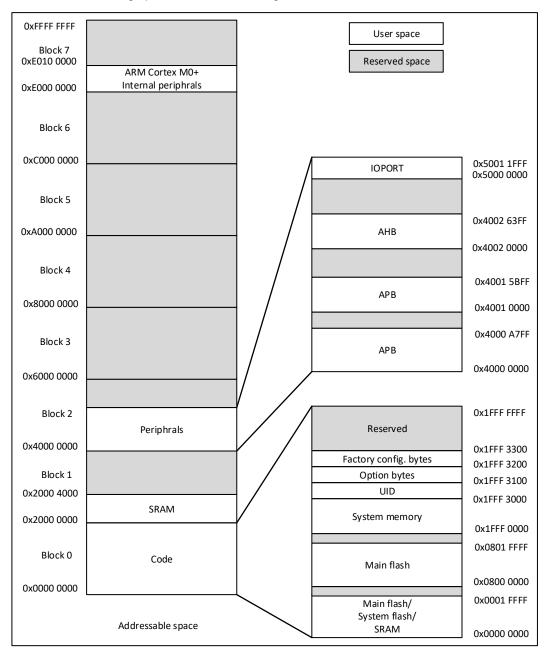

# 3. Memory and bus architecture

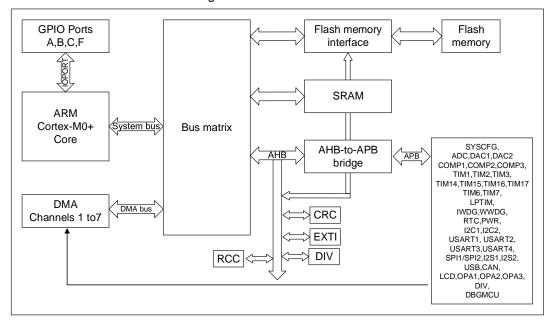

## 3.1. System architecture

The system consists of the following components:

- Two Masters

- Cortex-M0+

- Universal DMA

- Three Slaves

- Internal SRAM

- Internal Flash

- AHB with AHB-APB Bridge

Figure 3-1 System Architecture

#### ■ CPU system bus

This bus connects the Cortex-M0+ system bus to the bus matrix.

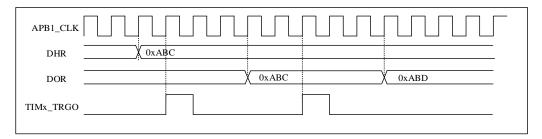

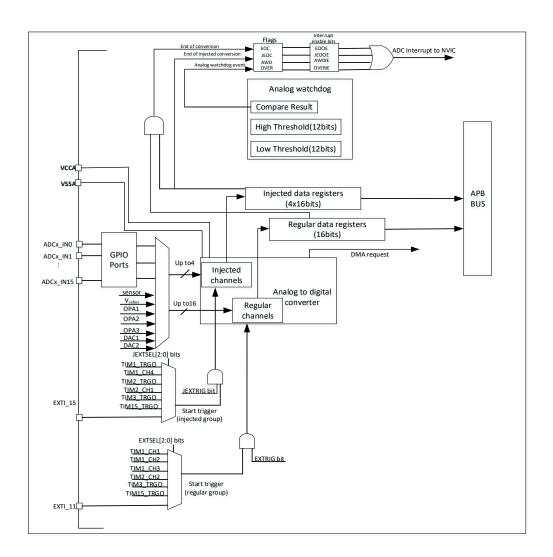

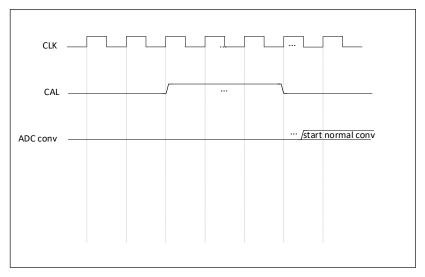

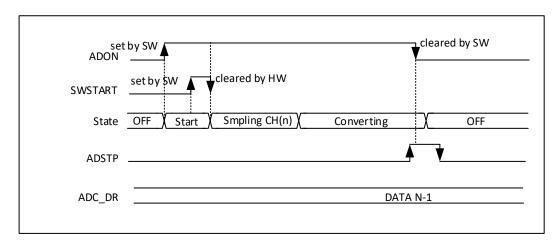

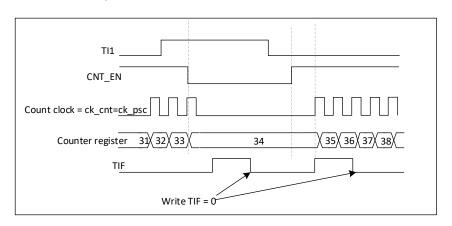

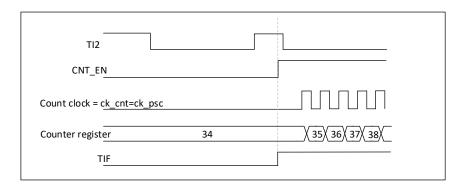

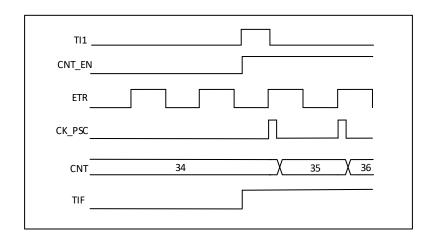

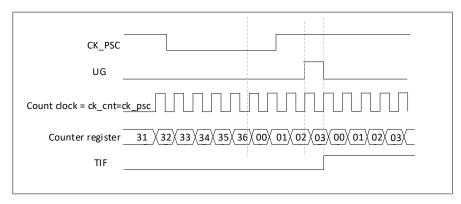

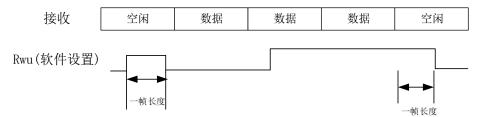

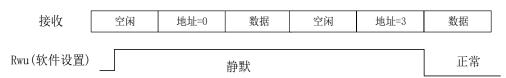

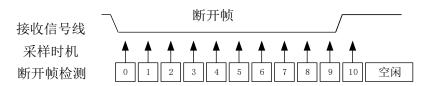

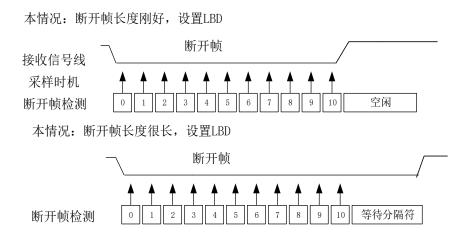

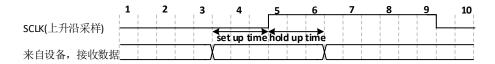

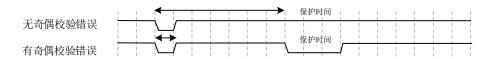

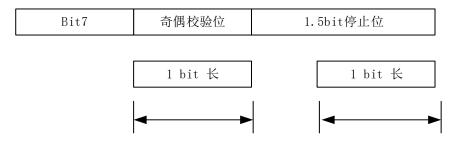

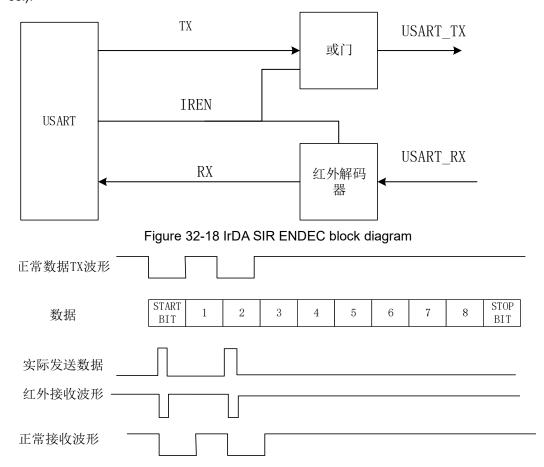

#### ■ DMA bus